Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:23.

- Sist endret 2025-01-23 15:02.

Jeg vil analysere hvordan utfordringen for strømforsyningsdesign møtes av DC-DC Technologies.

Kraftsystemdesignere står overfor konstant press fra markedet for å finne måter å få mest mulig ut av tilgjengelig strøm. På bærbare enheter forlenger høyere effektivitet batterilevetiden og legger mer funksjonalitet i mindre pakker. I servere og basestasjoner kan effektivitetsgevinster direkte spare infrastruktur (kjølesystemer) og driftskostnader (strømregninger). For å møte markedets krav forbedrer systemdesignere effektkonverteringsprosesser på flere områder, inkludert mer effektive bytte -topologier, pakkeinnovasjoner og nye halvlederenheter basert på silisiumkarbid (SiC) og galliumnitrid (GaN).

Trinn 1: Forbedring av Switching Converter Topology

For å dra full nytte av tilgjengelig kraft, bruker folk i økende grad design basert på koblingsteknologi i stedet for lineær teknologi. Bryterstrømforsyningen (SMPS) har en effektiv effekt på over 90%. Dette forlenger batterilevetiden til bærbare systemer, reduserer strømkostnadene for stort utstyr og sparer plass som tidligere ble brukt til kjøleribberkomponenter.

Å bytte til en byttet topologi har visse ulemper, og den mer komplekse designen krever at designere har flere ferdigheter. Designingeniører må være kjent med analoge og digitale teknologier, elektromagnetikk og lukket sløyfekontroll. Designere av kretskort (PCB) må ta mer hensyn til elektromagnetisk interferens (EMI) fordi høyfrekvente koblingsbølgeformer kan forårsake problemer i følsomme analoge og RF -kretser.

Før oppfinnelsen av transistoren ble det grunnleggende konseptet med omformet strømkonvertering foreslått: for eksempel induktivt utladningssystem av Kate-typen oppfunnet i 1910, som brukte en mekanisk vibrator for å implementere en flyback boost-omformer for et tenningssystem for biler.

De fleste standardtopologier har eksistert i flere tiår, men det betyr ikke at ingeniører ikke justerer standarddesign for å imøtekomme nye applikasjoner, spesielt kontrollløkker. Standardarkitekturen bruker en fast frekvens for å opprettholde en konstant utgangsspenning ved å mate tilbake en del av utgangsspenningen (spenningsmodusstyring) eller kontrollere den induserte strømmen (strømmodusstyring) under forskjellige belastningsforhold. Designere forbedrer seg stadig for å overvinne feilene i det grunnleggende designet.

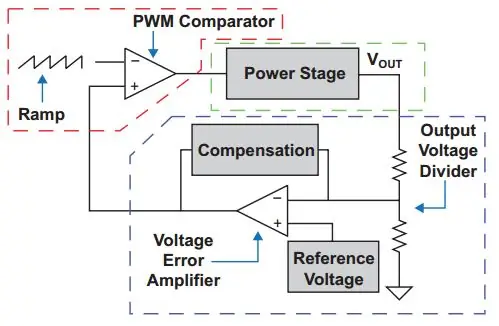

Figur 1 er et blokkdiagram av et grunnleggende lukket sløyfespenningsmodusstyringssystem (VMC). Strømstadiet består av en strømbryter og et utgangsfilter. Kompensasjonsblokken inkluderer en utgangsspenningsdeler, en feilforsterker, en referansespenning og en sløyfekompensasjonskomponent. En pulsbreddemodulator (PWM) bruker en komparator for å sammenligne feilsignalet med et fast rampesignal for å produsere en utgangspulssekvens som er proporsjonal med feilsignalet.

Selv om de forskjellige belastningene i VMC -systemet har strenge utgangsregler og er enkle å synkronisere med den eksterne klokken, har standardarkitekturen noen ulemper. Sløyfekompensasjon reduserer båndbredden til kontrollløyfen og bremser den forbigående responsen; feilforsterkeren øker driftsstrømmen og reduserer effektiviteten.

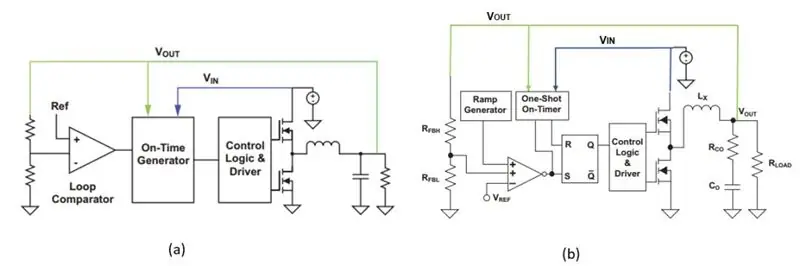

Den konstante tidsbestemmelsen (COT) gir god forbigående ytelse uten sløyfekompensasjon. COT-kontrollen bruker en komparator for å sammenligne den regulerte utgangsspenningen med referansespenningen: når utgangsspenningen er mindre enn referansespenningen, genereres en fast tidspuls. Ved lavdriftssykluser forårsaker dette at koblingsfrekvensen er veldig høy, så den adaptive COT-kontrolleren genererer en tid som varierer med inngangs- og utgangsspenningene, noe som holder frekvensen nesten konstant ved steady state. Texas Instruments D-CAP-topologi er en forbedring i forhold til den adaptive COT-tilnærmingen: D-CAP-kontrolleren legger til en rampespenning til tilbakemeldingens komparatorinngang, noe som forbedrer jitterytelsen ved å redusere støybåndet i applikasjonen. Figur 2 er en sammenligning av COT- og D-CAP-systemene.

Figur 2: Sammenligning av standard COT-topologi (a) og D-CAP-topologi (b) (Kilde: Texas Instruments) Det er flere forskjellige varianter av D-CAP-topologien for forskjellige behov. For eksempel bruker TPS53632 halvbro PWM-kontrolleren D-CAP+ -arkitekturen, som hovedsakelig brukes i applikasjoner med høy strøm og kan drive effektnivåer opp til 1MHz i 48V til 1V POL-omformere med en effektivitet så høy som 92%.

I motsetning til D-CAP, legger D-CAP+ tilbakemeldingssløyfen til en komponent som er proporsjonal med den induserte strømmen for presis slippkontroll. Den økte feilforsterkeren forbedrer nøyaktigheten av DC -belastningen under en rekke line- og belastningsforhold.

Kontrollerens utgangsspenning settes av den interne DAC. Denne syklusen starter når gjeldende tilbakemelding når feilspenningsnivået. Denne feilspenningen tilsvarer den forsterkede spenningsforskjellen mellom DAC -settpunktsspenningen og tilbakemeldingsutgangsspenningen.

Trinn 2: Forbedre ytelsen under lette belastningsforhold

For bærbare og bærbare enheter er det behov for å forbedre ytelsen under lette belastningsforhold for å forlenge batterilevetiden. Mange bærbare og bærbare applikasjoner er i lav-strøm "midlertidig hvilemodus" eller "hvilemodus" mesteparten av tiden, bare aktivert som svar på brukerinngang eller periodiske målinger, så minimer strømforbruket i standby-modus. Det er topp prioritet.

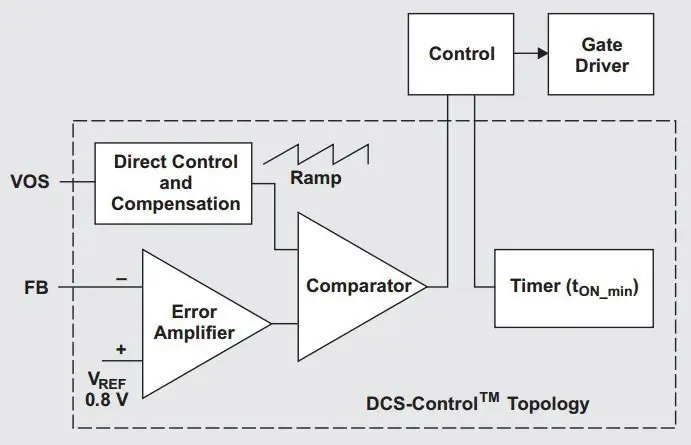

DCS-ControlTM (Direct Control to Seamless Transition to Energy Saver Mode) topologi kombinerer fordelene med tre forskjellige kontrollordninger (dvs. hysteresemodus, spenningsmodus og nåværende modus) for å forbedre ytelsen under lette belastningsforhold, spesielt overgang til Eller når forlater lett belastningstilstand. Denne topologien støtter PWM -moduser for middels og tung last, samt strømsparingsmodus (PSM) for lette laster.

Under PWM -drift opererer systemet med sin nominelle koblingsfrekvens basert på inngangsspenningen og styrer frekvensendringen. Hvis laststrømmen reduseres, bytter omformeren til PSM for å opprettholde høy effektivitet til den faller til en veldig lett belastning. Ved PSM synker koblingsfrekvensen lineært med laststrøm. Begge modusene styres av en enkelt kontrollblokk, så overgangen fra PWM til PSM er sømløs og påvirker ikke utgangsspenningen.

Figur 3 er et blokkdiagram av DCS-ControlTM. Kontrollsløyfen tar informasjon om endringen i utgangsspenningen og sender den direkte tilbake til den raske komparatoren. Komparatoren setter koblingsfrekvensen (som en konstant for driftstilstander i steady-state) og gir en umiddelbar respons på dynamiske belastningsendringer. Spenningsfeedback -sløyfen regulerer DC -belastningen nøyaktig. Det internt kompenserte reguleringsnettverket muliggjør rask og stabil drift med små eksterne komponenter og lave ESR -kondensatorer.

Figur 3: Implementering av DCS-ControlTM topologi i TPS62130 buck converter (kilde: Texas Instruments)

TPS6213xA-Q1 synkron brytereffektomformer er basert på DCS-ControlTM topologi og er optimalisert for POL-applikasjoner med høy effekttetthet. Den typiske 2,5 MHz koblingsfrekvensen tillater bruk av små induktorer og gir rask transient respons og høy utgangsspenning. TPS6213 opererer fra et inngangsspenningsområde på 3V til 17V og kan levere opptil 3A kontinuerlig strøm mellom 0,9V og 6V utgangsspenninger.

Anbefalt:

DIY -- Hvordan lage en edderkopprobot som kan kontrolleres ved hjelp av smarttelefon ved hjelp av Arduino Uno: 6 trinn

DIY || Hvordan lage en edderkopprobot som kan kontrolleres ved hjelp av smarttelefon ved hjelp av Arduino Uno: Mens du lager en edderkopprobot, kan du lære så mange ting om robotikk. Som å lage roboter er både underholdende og utfordrende. I denne videoen skal vi vise deg hvordan du lager en Spider -robot, som vi kan bruke ved hjelp av smarttelefonen vår (Androi

Få blind til å gjenkjenne ting ved å berøre ting rundt dem ved hjelp av MakeyMakey: 3 trinn

Gjør blinde gjenkjenne ting ved å berøre ting rundt dem ved hjelp av MakeyMakey: introduksjon Dette prosjektet tar sikte på å gjøre blindes liv lett ved å identifisere ting rundt dem gjennom berøringsfølelsen. Meg og min sønn Mustafa tenkte vi på å finne et verktøy for å hjelpe dem, og i perioden vi brukte MakeyMakey -maskinvaren til

Kontroll ledet over hele verden ved bruk av internett ved hjelp av Arduino: 4 trinn

Kontroll ledet over hele verden ved bruk av internett ved hjelp av Arduino: Hei, jeg er Rithik. Vi kommer til å lage en Internett -kontrollert LED ved hjelp av telefonen din. Vi kommer til å bruke programvare som Arduino IDE og Blynk. Det er enkelt, og hvis du lyktes kan du kontrollere så mange elektroniske komponenter du vilTing We Need: Hardware:

Overvåke akselerasjon ved bruk av Raspberry Pi og AIS328DQTR ved hjelp av Python: 6 trinn

Overvåke akselerasjon ved hjelp av Raspberry Pi og AIS328DQTR Bruke Python: Akselerasjon er begrenset, tror jeg i henhold til noen fysikklover.- Terry Riley En gepard bruker fantastisk akselerasjon og raske endringer i hastighet når jeg jager. Den raskeste skapningen i land en gang i blant bruker sitt høyeste tempo for å fange byttedyr. Den

Hvordan lage en drone ved hjelp av Arduino UNO - Lag en quadcopter ved hjelp av mikrokontroller: 8 trinn (med bilder)

Hvordan lage en drone ved hjelp av Arduino UNO | Lag en Quadcopter ved hjelp av mikrokontroller: Introduksjon Besøk min Youtube -kanal En Drone er en veldig dyr gadget (produkt) å kjøpe. I dette innlegget skal jeg diskutere hvordan jeg får det billig? Og hvordan kan du lage din egen slik til en billig pris … Vel, i India er alle materialer (motorer, ESCer