Innholdsfortegnelse:

- Trinn 1: Hva er Vivado HLS?

- Trinn 2: HLS videobibliotek

- Trinn 3: Syntetisering

- Trinn 4: Versjonering og annen informasjon for eksport

- Trinn 5: Eksporter til et Vivado IP -bibliotek

- Trinn 6: Syntese og eksportanalyse

- Trinn 7: Legge til IP -biblioteket i Vivado

- Trinn 8: Gjør en oppgradering

- Trinn 9: Ytterligere detaljer og informasjon

- Trinn 10: Output og Input

- Trinn 11: AXI Register Interfacing

- Trinn 12: Dataflow Pragma

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:25.

- Sist endret 2025-01-23 15:02.

Har du noen gang ønsket å behandle video i sanntid uten å legge til mye ventetid eller i et innebygd system? Noen ganger brukes FPGA (Field Programmable Gate Arrays) for å gjøre dette; Men å skrive videobearbeidingsalgoritmer på maskinvarespesifikasjonsspråk som VHDL eller Verilog er i beste fall frustrerende. Skriv inn Vivado HLS, Xilinx -verktøyet som lar deg programmere i et C ++ - miljø og generere maskinvarespesifikasjonens språkkode fra den.

Nødvendig programvare:

- Vivado HLS

- Vivado

- (Hvis du bruker AXI -registrene) Vivado SDK

(Valgfritt) Last ned Xilinx -eksempler her:

Xilinx HLS -videoeksempler

Trinn 1: Hva er Vivado HLS?

Vivado HLS er et verktøy som brukes til å gjøre c ++ - lignende kode til maskinvarestrukturer som kan implementeres på en FPGA. Den inkluderer en IDE for å gjøre denne utviklingen. Når du har fullført utviklingen av koden for HLS kan du eksportere din genererte IP i et format til bruk sammen med Vivado.

Last ned de vedlagte filene og legg dem nær der du skal lage prosjektet. (gi dem et nytt navn til "top.cpp" og "top.h" hvis de har et randomisert navn)

Trinn 2: HLS videobibliotek

HLS videobibliotek har dokumentasjon med referansedesign i denne artikkelen: XAPP1167En annen god ressurs er Xilinx Wiki -siden om den.

Start Vivado HLS.

Lag et nytt prosjekt.

Ta filene du lastet ned i forrige trinn, og legg dem til som kildefiler. (Merk: filene blir ikke kopiert til prosjektet, men forblir i stedet der de er)

Bruk deretter Bla gjennom -knappen for å velge toppfunksjonen.

På neste side velger du Xilinx -delen du bruker.

Trinn 3: Syntetisering

Løsning => Kjør C -syntese => Aktiv løsning

Etter ~ 227.218 sekunder, bør det gjøres. (Merk: din faktiske syntesetid vil variere avhengig av mange faktorer)

Trinn 4: Versjonering og annen informasjon for eksport

Versjonsnumre samhandler med Vivado for å få deg til å kunne oppdatere IP -en i et design. Hvis det er en mindre versjonsendring, kan den gjøres på plass mens store versjonsendringer krever at du manuelt legger til den nye blokken og fjerner den gamle. Hvis grensesnittene ikke har endret seg og versjonsoppdateringen er en mindre, kan oppdateringen være gjort helt automatisk ved å trykke på oppdateringens IP -knapp. Du kan kjøre "report_ip_status" i Vivado tcl -konsollen for å se statusen til IP -en din.

Angi versjonsnumre og annen informasjon i Løsning => Løsningsinnstillinger …

Alternativt kan disse innstillingene angis under eksporten.

Trinn 5: Eksporter til et Vivado IP -bibliotek

Løsning => Eksporter RTL

Hvis du ikke angav IP -bibliotekets detaljer i forrige trinn, kan du gjøre det nå.

Trinn 6: Syntese og eksportanalyse

På denne skjermen kan vi se statistikken om vår eksporterte modul, som viser at den oppfyller klokkeperioden vår på 10ns (100MHz) og hvor mye av hver ressurs den bruker.

Med en kombinasjon av dette, vår synteserapport og vår Dataflow -analyse, kan vi se at det tar 317338 klokkesykluser * 10ns klokkeperiode * 14 rørledningstrinn = 0,04442732 sekunder. Det betyr at den totale ventetiden som er lagt til av vår bildebehandling, er mindre enn en tyvendedel av et sekund (når den klokkes til den målrettede 100MHz).

Trinn 7: Legge til IP -biblioteket i Vivado

For å bruke din syntetiserte IP -blokk må du legge den til i Vivado.

I Vivado kan du legge til et IP-depot i prosjektet ditt ved å gå til IP-katalogen og høyreklikke på "Legg til depot …"

Naviger til Vivado HLS -prosjektkatalogen og velg løsningskatalogen din.

Den bør rapportere IP -en som den fant.

Trinn 8: Gjør en oppgradering

Noen ganger må du gjøre endringer i HLS -blokken etter å ha inkludert den i et Vivado -design.

For å gjøre dette kan du gjøre endringene og syntetisere på nytt og eksportere IP -adressen med et høyere versjonsnummer (se detaljer i tidligere trinn om større/mindre versjonsnummerendringer).

Etter endring av eksport av den nye versjonen, oppdater IP -lagrene dine i Vivado. Dette kan enten gjøres når Vivado merker at IP -en har endret seg i depotet, eller aktivert manuelt. (Vær oppmerksom på at hvis du oppdaterer IP -lagrene dine etter oppstart, men før eksporten er fullført i HLS, vil IP -adressen midlertidig ikke være der, vent på at den er ferdig og oppdateres igjen.)

På dette tidspunktet skal det vises et vindu med informasjon om at en IP har blitt endret på disken og gir deg muligheten til å oppdatere den med en "Oppgrader valgt" -knapp. Hvis endringen var en mindre versjonsendring og ingen av grensesnittene ble endret, Hvis du trykker på den knappen, erstattes den gamle IP -adressen automatisk med den nye, ellers kan det være nødvendig med mer arbeid.

Trinn 9: Ytterligere detaljer og informasjon

Følgende trinn gir mer informasjon om hvordan HLS -syntese fungerer og hva du kan gjøre med den.

For et eksempel på et prosjekt som bruker en HLS -syntetisert IP -blokk, se denne instruksen.

Trinn 10: Output og Input

Utganger og innganger til den endelige IP -blokken bestemmes ut fra en analyse som synthesizeren gjør av datastrømmen inn og ut av toppfunksjonen.

I likhet med i VHDL eller verilog lar HLS deg spesifisere detaljer om tilkoblingene mellom IP. Disse linjene er eksempler på dette:

ugyldig image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE akseport = video_in bunt = INPUT_STREAM #pragma HLS INTERFACE akseport = video_out pakke = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14 #pragma HLS INTERCACE = portx_yTX_1

Du kan se hvordan portene som vises på IP -blokken påvirkes av disse direktivene.

Trinn 11: AXI Register Interfacing

For å få input/output til/fra IP -blokken til PS er en god måte å gjøre dette på via et AXI -grensesnitt.

Du kan spesifisere dette i HLS -koden din, inkludert forskyvningene som skal brukes for å få tilgang til verdien senere slik:

ugyldig image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Når du er koblet til riktig i Vivado, kan du få tilgang til verdiene ved hjelp av denne koden i Vivado SDK:

#include "parameters.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Dette vil få deg til å ende opp med 42 i x og 0xdeadbeef i y

Trinn 12: Dataflow Pragma

I #pragma DATAFLOW endres måten som koden er implementert på fra normal C ++. Koden er pipelined slik at alle instruksjonene kjører til enhver tid i forskjellige deler av dataene (Tenk på det som en samlebånd i en fabrikk, hver stasjon jobber kontinuerlig med å gjøre en funksjon og overføre den til neste stasjon)

fra bildet kan du se at hvert av direktivene

Til tross for at de ser ut til å være normale variabler, blir img -objekter faktisk implementert som små buffere mellom kommandoene. Å bruke et bilde som inngang til en funksjon "forbruker" det og gjør det ikke lenger brukbart. (Derfor behovet for dupliserte kommandoer)

Anbefalt:

MIDI-kontrollert trinnmotor med direkte digital syntese (DDS) brikke: 3 trinn

MIDI-kontrollert trinnmotor med direkte digital syntese (DDS) -brikke: Har du noen gang hatt en dårlig ide om at du BARE måtte gjøre om til et miniprosjekt? Vel, jeg lekte med en skisse jeg hadde laget for Arduino Due med sikte på å lage musikk med en AD9833 Direct Digital Synthesis (DDS) -modul … og på et tidspunkt tenkte jeg og spørre

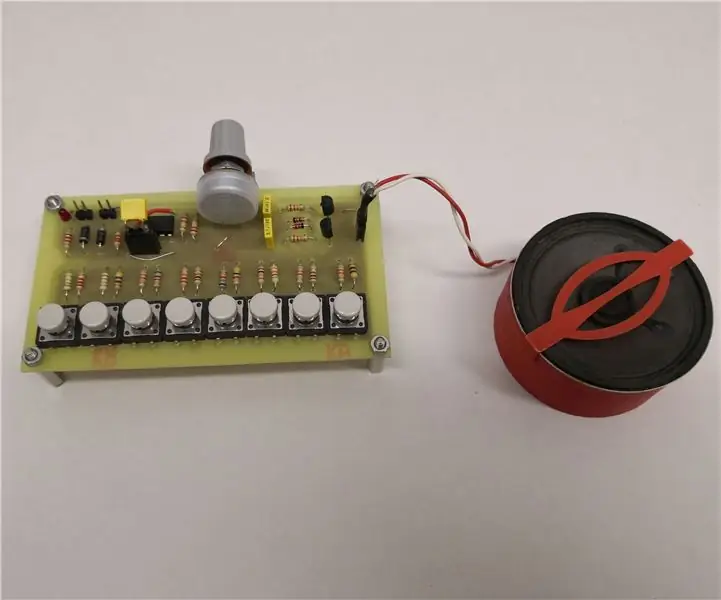

Fantastisk analog syntese/organ som bare bruker diskrete komponenter: 10 trinn (med bilder)

Awesome Analog Synthesizer/Organ Using Only Discrete Components: Analoge synthesizere er veldig kule, men også ganske vanskelige å lage. Så jeg ønsket å lage en så enkel som den kan bli, så dens funksjon kan være lett å forstå. For at den skal fungere, kan du trenger noen få grunnleggende sub-kretser: En enkel oscillator med resis

Min første syntese: 29 trinn (med bilder)

Min første syntese: Barnesynten kom til da jeg satt bøyd over et sammenfiltret rot av synthesizertråder. Vennen min Oliver kom bort, vurderte situasjonen og sa: "Du vet at du har lykkes med å lage verdens mest kompliserte barneleke." Mens min første

Phono -Chronoxyle - en 360 graders syntese: 3 trinn (med bilder)

Phono -Chronoxyle - en 360 graders syntese: Julien Signolet -skulptør basert fra Paris og musiker Mathias Durand henvendte seg til meg for en interaktiv lydinstallasjon på Parc Floral i Paris for Nuit Blanche 2019. Installasjonen ville være utenfor døren og jeg ville ikke være til stede under det i

La oss bygge en SN76489 USB MIDI -syntese med Arduino Nano: 7 trinn

La oss bygge en SN76489 USB MIDI Synth med Arduino Nano: Har du noen gang ønsket å bygge din egen synthesizer basert på gamle chip-melodier fra 80-tallet? Spill enkle polyfoniske låter som høres ut akkurat som disse gamle Sega Master System- og Megadrive -videospillene hørtes ut som? Jeg har, så jeg bestilte noen få SN76489 -brikker fra eb