Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:25.

- Sist endret 2025-01-23 15:02.

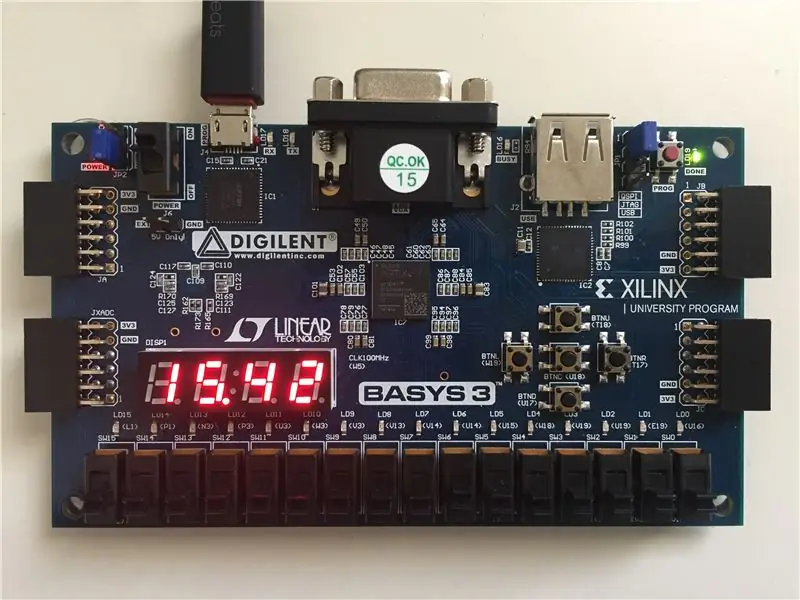

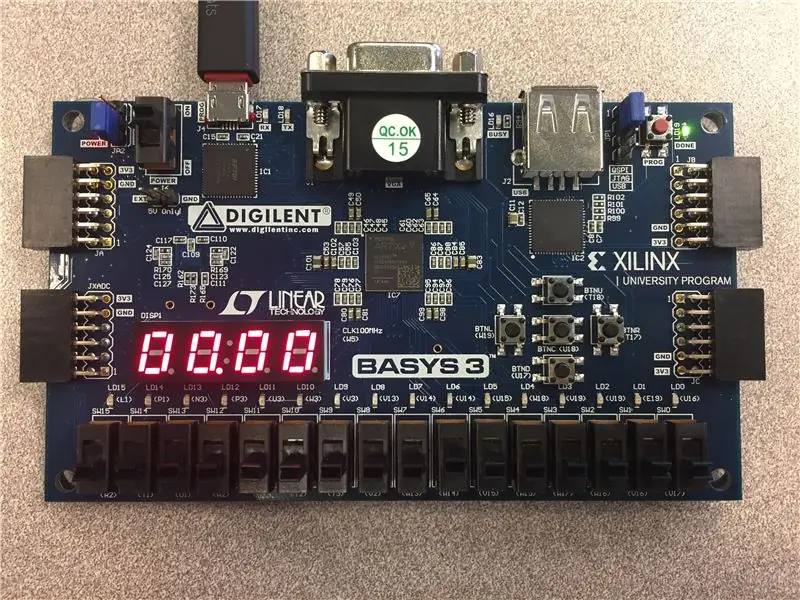

Dette er en opplæring om hvordan du lager en stoppeklokke ved hjelp av VHDL og et FPGA-kretskort, som et Basys3 Atrix-7-kort. Stoppeklokken kan telle fra 00,00 sekunder til 99,99 sekunder. Den bruker to knapper, en for start/stopp -knappen og en for tilbakestillingsknappen. Tallene vises på brettets sjusegmentdisplay ved hjelp av dets anoder og katoder. Det er tre forskjellige filer som trengs for å få denne stoppeklokken til å fungere.

Trinn 1: Maskinvare/programvare

- Basys3 Atrix-7 FPGA Board

- Vivado Design Suite fra Xilinx

- USB 2.0 A Hann til Micro-B Hann

Trinn 2: Blokkdiagram

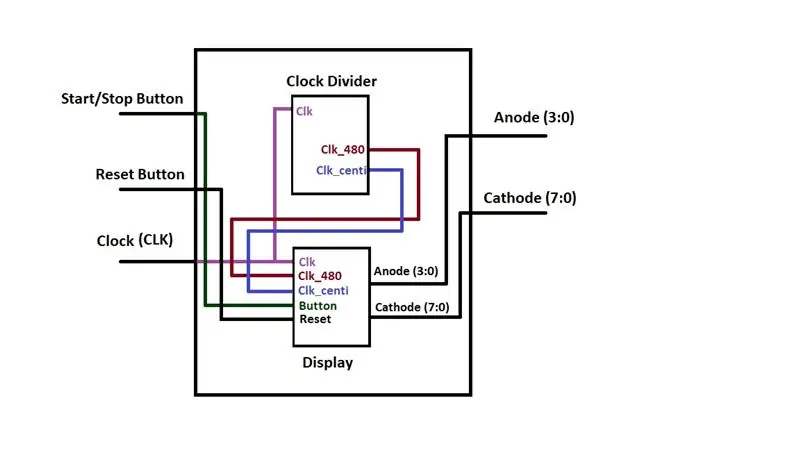

Den totale stoppeklokken har tre innganger og to utganger. De tre inngangene er start/stopp, tilbakestilling og klokke. Start/stopp og tilbakestilling er knapper og klokken er brettets 100MHz klokke. De to utgangene er anoder og katoder for displayet med syv segmenter.

Den første modulen (klokkedeleren) har en inngang og to utganger. Inngangen er brettets 100MHz klokke og utgangene er to separate klokker, en som kjører på 480Hz og en annen som kjører 0,5MHz.

Den andre modulen (display) har fem innganger og to utganger. Inngangene er brettets 100MHz -klokke, de to klokkene fra klokkedelermodulen, og start/stopp- og tilbakestillingsknappene. Utgangene er anoder og katoder.

Den siste modulen (modellert av hele blokkdiagrammet) har tre innganger og to utganger. Dette er filen som bringer alt sammen. Inngangene er brettets 100MHz og knappene start/stopp og tilbakestilling. Utgangene er anoder og katoder som styrer syv-segmentet. Alle innganger og utganger er fysisk på tavlen for den siste modulen.

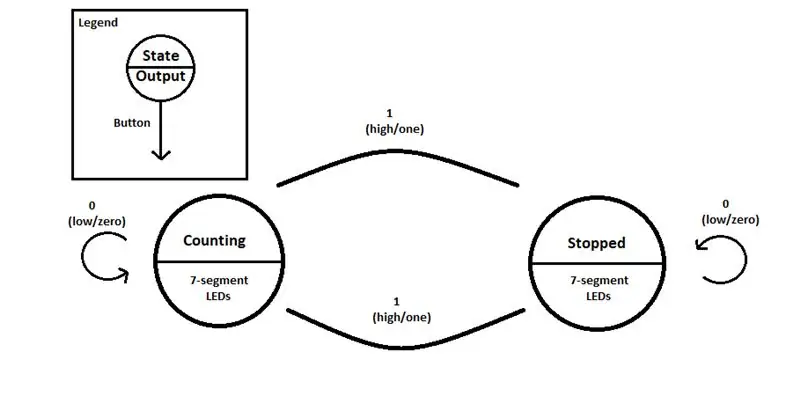

Trinn 3: Oppgi diagram

Bildet ovenfor viser tilstandsdiagrammet for hvordan stoppeklokken fungerer. Trykk på tilbakestillingsknappen har ingen innvirkning på stoppeklokken. Neste tilstand bestemmes av start/stopp -knappen. Starten/stoppet er "HØYT" når det trykkes ned, men ikke når det holdes nede, og "LAVT" når knappen har slått tilbake eller holdt nede etter å ha blitt "HØY" et øyeblikk.

Hvis stoppeklokken teller og start/stopp -knappen går "HØY", slutter den å telle. Hvis stoppeklokken stoppes og start/stopp -knappen går "HØY", begynner den å telle igjen. For begge delstatene, hvis start/stopp -knappen er "LAV", vil den forbli i tilstanden den er i for øyeblikket.

Trinn 4: Clock Divider Module

Klokkedelermodulen har en inngang, brettets 100MHz klokke og to utganger, 480Hz og 0.5MHz klokker. 480Hz-klokken brukes til å holde alle lysdiodene på sjusegmentsdisplayet "på" samtidig ved å bytte raskt gjennom de fire. 0,5 MHz-klokken brukes til at stoppeklokken faktisk skal telle med centisekunder.

Trinn 5: Skjermmodul

Denne skjermmodulen har fem innganger, brettets 100MHz klokke, de to klokkene fra klokkemodulen, start/stopp og tilbakestillingsknappene, og to utganger, anoder og katoder. Denne modulen har også "logikken" for hvordan stoppeklokken teller og inkorporerer den endelige tilstandsmaskinen.

Trinn 6: Bindingsmodul

Denne siste modulen er den som bringer de to andre modulene sammen. Den har tre innganger, brettets 100MHz klokke og start/stopp og tilbakestillingsknappene, og to utganger, anoder og katoder. 100MHz -klokken går til klokkedelermodulen og skjermmodulen, og start/stopp- og tilbakestillingsknappene går til skjermmodulen. Utgangene til klokkedelermodulen (480Hz og 0,5MHz) går til de to klokkeinngangene på displaymodulen. Utgangene til displaymodulen (anoder og katoder) går til den siste modulens utganger.

Trinn 7: Begrensninger

De to inngangene kan være hvilken som helst knapp på Basys3 Atrix-7 FPGA-kortet, og utgangene kommer til å være de fire anodene og de åtte katodene (fordi du også vil ha et desimalpunkt mellom sekunder og millisekunder) for syv-segmentet.

Trinn 8: Ferdig

Last opp programmet til ditt Basys3 Atrix-7 FPGA Board og trykk på start/stopp-knappen for å få stoppeklokken i gang!

Anbefalt:

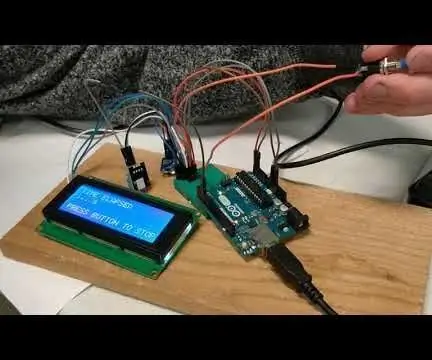

Hvordan lage en stoppeklokke ved hjelp av Arduino: 8 trinn (med bilder)

Hvordan lage en stoppeklokke ved hjelp av Arduino: Dette er en veldig enkel Arduino 16*2 LCD -skjermstoppur ……….. /ZenoModiff

Grunnleggende stoppeklokke ved bruk av VHDL og Basys3 Board: 9 trinn

Grunnleggende stoppeklokke ved bruk av VHDL og Basys3 -kort: Velkommen til instruksjonene om hvordan du bygger en stoppeklokke ved hjelp av grunnleggende VHDL- og Basys 3 -kort. Vi gleder oss til å dele prosjektet vårt med deg! Dette var et avsluttende prosjekt for kurs CPE 133 (Digital Design) på Cal Poly, SLO høsten 2016. Prosjektet vi bygde

Arduino stoppeklokke: 4 trinn (med bilder)

Arduino stoppeklokke: Denne instruksjonsfilen viser deg hvordan du lager en stoppeklokke av en Arduino

Enkel Arduino -klokke / stoppeklokke: 6 trinn (med bilder)

Enkel Arduino -klokke / stoppeklokke: Denne " instruerbare " vil vise og lære deg hvordan du lager en enkel Arduino Uno -klokke som også fungerer som stoppeklokke i bare noen få, enkle trinn

VHDL Ett minutts stoppeklokke: 5 trinn

VHDL One Minute Stopwatch: Dette er en opplæring i hvordan du bygger et stoppeklokke på ett minutt ved hjelp av VHDL og et Basys 3 -kort. En slik enhet er ideell for spill der hver spiller har maksimalt ett minutt på seg. Stoppeklokken viser nøyaktig sekunder og millisekunder