Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:25.

- Sist endret 2025-01-23 15:02.

Dette er en opplæring i hvordan du bygger en ett -minutters stoppeklokke ved hjelp av VHDL og et Basys 3 -kort. En slik enhet er ideell for spill der hver spiller har maksimalt ett minutt på seg. Stoppeklokken viser nøyaktig sekunder og millisekunder på sju segmenters display, med start på 0 sekunder og 0 millisekunder, opptil 60 sekunder og 0 millisekunder. To knapper brukes også: den sentrale knappen, som brukes til å starte, stoppe og fortsette timeren, og den høyre knappen, brukes til å starte timeren på nytt. Når enheten sammenlignes side om side med den innebygde stoppeklokken til en smarttelefon, er klokkens nøyaktighet merkbar.

Trinn 1: Skaff maskinvare/programvare

1. Basys 3 Artix-7 FPGA Trainer Board fra Digilent med Micro-USB til USB-kabel

2. Vivado 2016.2 Design Suite fra Xilinx

Trinn 2: Blokkdiagram

Denne kretsen er konstruert atferdsmessig og bruker innebygde Xilinx-komponenter, men kan også beskrives strukturelt, som vist av det generelle strukturelle diagrammet ovenfor. Fra diagrammet kan det sees at kretsen drives av to frekvensdelere. En av frekvensdelerne kjører på 1 centisekund og driver katodetelleren som brukes som tallene som vises på syv-segmentet. Den andre frekvensdeleren kjører på 240Hz og brukes til å drive anodetelleren som roterer gjennom anodene slik at alle tallene vises riktig på syv-segmentet. Koderen tar katodelogikken fra katodetelleren og anodelogikken fra anodetelleren, og koder den til utgangens katode og anode som kjører syvsegmentet. Funksjonen til denne koderen er at katodeutgangen endres hver gang anodeutgangen endres. Katodeutgangen kan ikke kjøres uavhengig av telleren fordi anodene må rotere gjennom de fire separate sifrene.

Trinn 3: Prosjektmodul

For det første opprettes en prosessblokk for CEN slik at når et knappetrykk oppdages, vil ENABLE veksle. Dette fungerer som stopp/start av katodetelleren.

I den neste prosessblokken settes centisekund- og 240Hz -klokkesignalene slik at deres respektive tellere øker med 1 hver gang den interne 100mHz -klokken når en stigende kant. Når centisekundtelleren når 500000, vil den tilbakestilles til 0. I mellomtiden vil 240Hz -telleren nullstilles når tellingen når 41667.

For katodeseksjonen i koden, hvis ENABLE er '0', vil katodetellingen stoppe. Hvis tilbakestillingsknappen trykkes i løpet av denne tiden, tilbakestilles alle tellinger til "0000". I mellomtiden, hvis AKTIVER er '1', vil katodetellingen fortsette til katodeantallet når 60,00, der det utløser stoppsignalet til å være '1'. Stoppsignalet går tilbake til CEN -prosessblokken og får ENABLE til å være '0' mens stoppsignalet er '1' og endres ikke før tilbakestillingsknappen trykkes.

Til slutt er displayet med syv segmenter satt opp ved å ha de 4 anodene riktig forbundet med hver av deres 8 katoder for å vise sine respektive sifre 0-9 samtidig.

Trinn 4: Begrensninger

Denne begrensningsfilen kobler de spesifiserte inngangene og utgangene fra VHDL til de nødvendige, fysiske delene av Basys -kortet. For dette prosjektet inkluderer komponentene de fire anodene og hver av deres åtte katoder for displayet med syv segmenter, den interne 100 mHz klokken, midtknappen og den høyre knappen.

Trinn 5: Test

Når du har fullført koden, kan du nå programmere FPGA via USB -kabelen. Displayet med syv segmenter skal vise 0,00. Test for å se om knappene fungerer ved å trykke på den sentrale knappen for å starte timeren til den når 60,00 og stopper; når som helst i mellom kan du trykke på den sentrale knappen igjen for å sette den på pause. Når den er satt på pause, kan du trykke på høyre knapp for å tilbakestille timeren til 0,00. Hvis alt fungerer som det skal, gratulerer med at du nettopp har bygd en timer på ett minutt!

Anbefalt:

Arduino Leonardo stoppeklokke: 3 trinn

Arduino Leonardo Stoppeklokke: Kreditt: https://www.instructables.com/id/Arduino-Stopwatch … Denne stoppeklokke-designen stammer fra lenken ovenfor, som er en stoppeklokke som teller fra 1, mens denne teller ned fra 60 sekunder . Det meste av koden jeg har brukt følger originalen

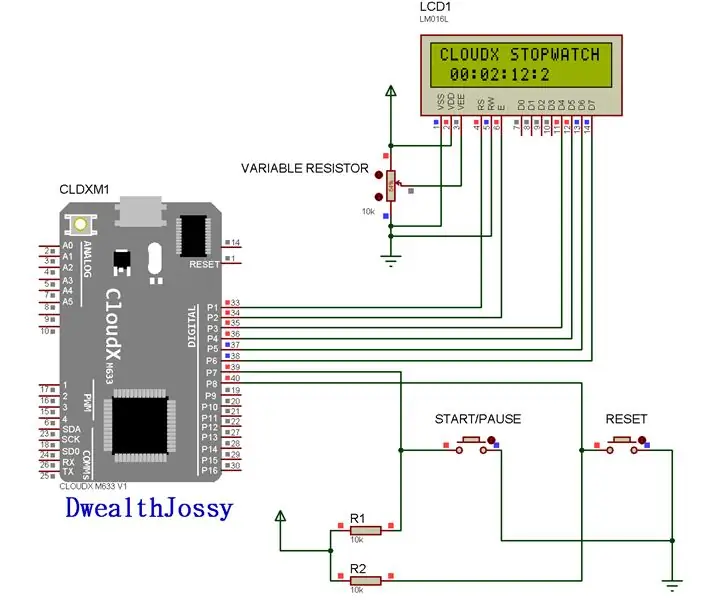

Enkel CloudX M633 digital stoppeklokke: 4 trinn

Enkel CloudX M633 digital stoppeklokke: I dette prosjektet skal vi lage en versjon av en digital klokke som kan holde oversikt over timer, minutter og sekunder, akkurat som et stoppeklokke på mobiltelefonen! Vi skal bruke en LCD for å vise tiden

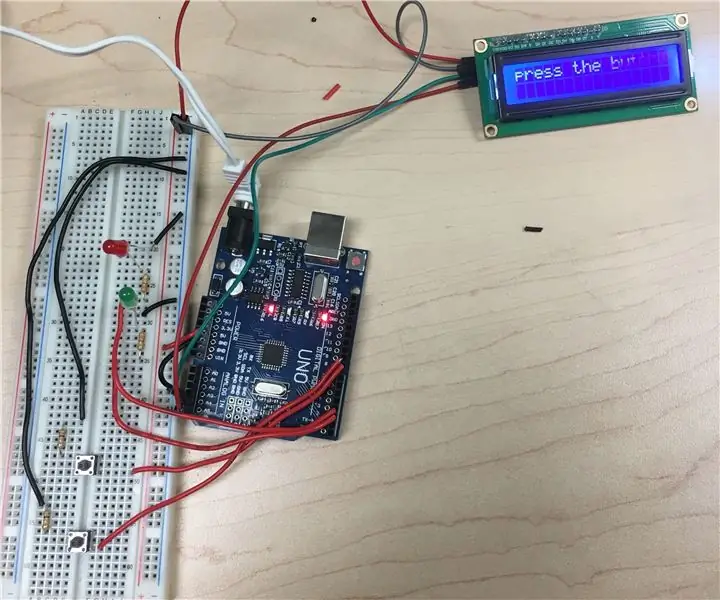

Arduino stoppeklokke ved bruk av I2C LCD: 5 trinn

Arduino stoppeklokke ved bruk av I2C LCD: I dette prosjektet skal jeg lære deg å bruke en LCD -skjerm og en Arduino som en interaktiv stoppeklokke. Når prosjektet er ferdig med koden, skal det se ut som bildet ovenfor. Gå til neste trinn for å lære hvor du skal begynne

Grunnleggende stoppeklokke ved bruk av VHDL og Basys3 Board: 9 trinn

Grunnleggende stoppeklokke ved bruk av VHDL og Basys3 -kort: Velkommen til instruksjonene om hvordan du bygger en stoppeklokke ved hjelp av grunnleggende VHDL- og Basys 3 -kort. Vi gleder oss til å dele prosjektet vårt med deg! Dette var et avsluttende prosjekt for kurs CPE 133 (Digital Design) på Cal Poly, SLO høsten 2016. Prosjektet vi bygde

VHDL stoppeklokke: 8 trinn (med bilder)

VHDL Stoppeklokke: Dette er en opplæring i hvordan du lager en stoppeklokke ved hjelp av VHDL og et FPGA-kretskort, som et Basys3 Atrix-7-kort. Stoppeklokken kan telle fra 00,00 sekunder til 99,99 sekunder. Den bruker to knapper, en for start/stopp -knappen og en for