Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:23.

- Sist endret 2025-01-23 15:02.

I denne instruksen skal vi designe en enkel VGA -kontroller i RTL. VGA -kontrolleren er den digitale kretsen designet for å drive VGA -skjermer. Den leser fra Frame Buffer (VGA Memory) som representerer rammen som skal vises, og genererer nødvendige data og synkroniseringssignaler for visningsformål.

Hvis du leter etter Verilog/System verilog -kode: Besøk bloggen min VGA -kontroller og videosystem i Verilog

Trinn 1: Grensesnitt til en VGA -kontroller

Følgende er hovedgrensesnittsignalene i en VGA -kontroller

- Pixel Clock eller VGA Clock

- HSYNC og VSYNC signaler

For den valgte VGA -skjermen må du først beregne frekvensen til Pixel Clock som trengs for å kjøre den. Det avhenger av 3 parametere: Totale horisontale piksler, Totale vertikale piksler, Skjermoppdateringshastighet.

Vanligvis er F = THP * TVP * Oppdateringsfrekvens

Finn dokumentasjonen om pikselklokke som trengs for forskjellige VGA -skjermer, i vedlagte RAR.

HSYNC- og VSYNC -signaler genereres fra Pixel -klokken. Tidspunktet for HSYNC- og VSYNC -signaler avhenger av antall parametere: Horisontal og vertikal frontporch, horisontal og vertikal bakporch, horisontal og vertikal displaypiksel, horisontal og vertikal synkroniseringspulsbredde og polaritet.

Disse parameterne er standardisert for en valgt VGA -skjerm. Finn disse dokumentene i vedlagte RAR.

Disse parameterne er konfigurerbare parametere i vår VGA -kontroller -IP.

Trinn 2: Integrering av VGA -kontrolleren med en VGA -skjerm

Figuren viser hvordan du integrerer VGA -kontrolleren med en VGA -skjerm. Du trenger to komponenter til for å fullføre systemet:

- Frame Buffer: Minne som inneholder rammen som skal vises.

- Video DAC: DAC som konverterer digitale RGB -data og driver VGA -skjermen med analoge RGB -signaler på passende spenningsnivå.

En av de enkleste og mest populære Video DAC -ene er ADV7125. Det er en 8-bits DAC som konverterer digitale RGB-ord til 0-0,7 V analoge signaler og driver VGA-skjermen.

Trinn 3: Design av rammebuffer

Det er minnet som "lagrer" bildet som skal vises. Det er vanligvis en RAM eller noen ganger ROM. Vi vil diskutere hvordan du designer en rammebuffer for å representere et bilde. Rammebuffer sender denne digitale informasjonen til en Video DAC på kommando fra VGA -kontrolleren.

Først må vi bestemme pikseldybden som trengs. Det bestemmer kvaliteten på bildet, de forskjellige fargene en piksel kan representere. For en 8-bits DAC må vi representere de primære fargekomponentene i en piksel: R, G og B i 8 bits hver. Det betyr at en piksel er 24-bit.

Hver piksel lagres på en sammenhengende måte i Frame Buffer -minnelokasjoner.

Anta at et bilde som skal vises er 800x600 piksler.

Derfor er Frame Buffer nødvendig 800x600 = 480000 x 24 bits minne

Total størrelse på minnet er 800x600x24 = 1400 kB ca.

Hvis svart -hvitt bilde, 800x600x1 = 60 kB ca.

Blokk -RAM -er brukes kanskje til å representere en rammebuffer i Xilinx FPGA -er.

Trinn 4: Merknader

- Ytterligere signaler er nødvendig på VGA -kontrolleren, avhengig av hvilken DAC som er valgt. Jeg har brukt ADV7125.

- Legg til syklusforsinkelser gjennom flip-flops på VSYNC og HSYNC før du kjører VGA-skjerm. Dette er på grunn av DAC og minnetidsforsinkelser. Pixelsignalene bør synkroniseres med HSYNC og VSYNC. I mitt tilfelle var det 2 syklus forsinkelser.

- Hvis rammebuffer av gitt størrelse ikke kan utformes på FPGA på grunn av begrensning av blokkstørrelse, bruker du mindre minne til å representere bildet og bare redigerer koden for å rulle over adressen på det tilgjengelige minnets grense, i stedet for hele rammens grense. Dette vil replikere det samme bildet igjen og igjen langs hele skjermen. En annen metode er pikselskala der hver piksel replikeres for å vise hele bildet i fullskjerm, i en mindre oppløsning. Dette kan gjøres ved å justere adresseinkrementeringslogikken i koden.

- IP-en er fullstendig bærbar på tvers av alle FPGA-er og er tidsbestemt opptil 100 MHz på Virtex-4 FPGA.

Trinn 5: Vedlagte filer

RAR inneholder:

- VGA -kontrollerkode

- PDF -filer med VGA -standarder.

Anbefalt:

Design av en programmerbar avbryterkontroller i VHDL: 4 trinn

Design av en programmerbar interrupt -kontroller i VHDL: Jeg er overveldet over den typen svar jeg får i denne bloggen. Takk gutter for at du besøkte bloggen min og motiverte meg til å dele min kunnskap med deg. Denne gangen skal jeg presentere designet til en annen interessant modul vi ser i alle SOC -er - Interrupt C

Design av I2C Master i VHDL: 5 trinn

Design av I2C Master i VHDL: I denne instruksjonsboken diskuteres det å designe en enkel I2C -master i VHDL. MERK: klikk på hvert bilde for å se hele bildet

Design av SPI Master i VHDL: 6 trinn

Design av SPI Master i VHDL: I denne instruksen skal vi designe en SPI Bus Master fra bunnen av i VHDL

Design av UART i VHDL: 5 trinn

Design av UART i VHDL: UART står for Universal Asynchronous Receiver Transmitter. Det er den mest populære og enkleste seriekommunikasjonsprotokollen. I denne instruksen lærer du hvordan du designer en UART -modul i VHDL

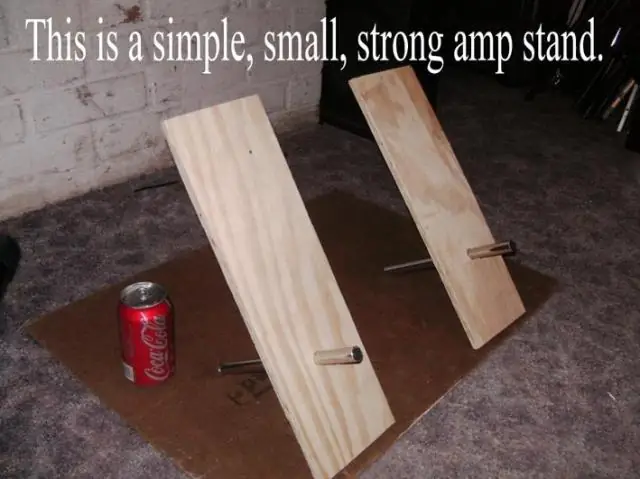

Guitar Amp Tilt Stand - "African Chair" Design - Enkel, liten, sterk, enkel, gratis eller ekte billig: 9 trinn

Guitar Amp Tilt Stand - "African Chair" Design - Enkel, liten, sterk, enkel, gratis eller ekte billig: Guitar Amp Tilt Stand - For lett - enkel, liten, sterk, gratis eller skikkelig billig. For alle forsterkere, til og med store skap med separat hode. Bare lag brett og rør i størrelsen, og du trenger for nesten alt utstyr du ønsker