Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:22.

- Sist endret 2025-01-23 15:02.

Jeg skriver dette instruerbart, fordi jeg syntes det var litt vanskelig å få noen referanse -VHDL -kode for å lære og begynne å designe en hurtigbufferkontroller. Så jeg designet en cache -kontroller selv fra bunnen av, og testet den vellykket på FPGA. Jeg har presentert en enkel direkte kartlagt cache-kontroller her, samt modellert et helt prosessor-minnesystem for å teste cachekontrolleren. Jeg håper dere synes dette er nyttig som en referanse for å designe deres egne hurtigbufferkontrollere.

Trinn 1: Spesifikasjoner

Dette er hovedspesifikasjonene til hurtigbufferkontrolleren vi skal designe:

- Direkte kartlagt. (gå til denne lenken hvis du ser etter Associative Mapped Cache Controller)

- Enbanket, blokkerende hurtigbuffer.

- Gjennomgående retningslinjer for skrivehits.

- Ikke-skriv tildeling eller Skriv rundt retningslinjer for skrivefeil.

- Ingen skrivebuffer eller andre optimaliseringer.

- Tag Array er inkorporert.

I tillegg til det, vil vi også designe et cacheminne og et hovedminnesystem.

Standard (konfigurerbare) spesifikasjoner for hurtigbufferminnet:

- 256 Bytes enkeltbanket hurtigbuffer.

- 16 Cache Lines, hver Cache Line (Block) = 16 Bytes.

Spesifikasjonene til hovedminnet:

- Synkron lese/skrive minne.

- Multibanket interleaved minne - fire minnebaner.

- Hver bankstørrelse = 1 kB hver. Derfor er total størrelse = 4 kB.

- Word (4 Bytes) adresserbart minne med 10-biters adressebuss.

- Høyere båndbredde for lesing. Les databredde = 16 Bytes i en klokkesyklus.

- Skriv databredde = 4 Bytes.

MERK: sjekk min nyere instruerbare hvis du leter etter 4-veis assosiativ cache-kontrollerdesign

Trinn 2: RTL -visning av hele systemet

Komplett RTL -representasjon av toppmodulen er vist på figuren (unntatt prosessoren). Standard spesifikasjoner for bussene er:

- Alle databusser er 32-biters busser.

- Adressebuss = 32-biters buss (men bare 10 bits kan adresseres her av minnet).

- Datablokk = 128 bits (Wide Bandwidth Bus for Read).

- Alle komponenter drives av samme klokke.

Trinn 3: Testmiljø

Toppmodulen ble testet ved hjelp av en testbenk, som ganske enkelt modellerer en prosessor uten rørledning (Fordi det ikke er lett å designe en hel prosessor !!). Testbenken genererer ofte forespørsler om lese/skrive data til minnet. Dette håner typiske "Last" og "Lagre" instruksjoner, vanlig i alle programmer som utføres av en prosessor. Testresultatene bekreftet funksjonaliteten til hurtigbufferkontrolleren. Følgende er teststatistikken observert:

- Alle Les/skriv miss og treffsignaler ble generert riktig.

- Alle operasjoner med lese/skrive data var vellykkede.

- Det er ikke oppdaget problemer med datainkoherens/inkonsekvens.

- Designet ble vellykket timingbekreftet for en maks. Klokke Driftsfrekvens = 110 MHz i Xilinx Virtex-4 ML-403 Board (hele systemet), 195 MHz for Cache Controller alene.

- Blokk -RAM ble utledet for hovedminnet. Alle andre matriser ble implementert på LUT.

Trinn 4: Vedlagte filer

Følgende filer er vedlagt her med denne bloggen:

- . VHD -filer med Cache Controller, Cache Data Array, Main Memory System.

- Test benk.

- Dokumentasjon på Cache Controller.

Merknader:

- Gå gjennom dokumentasjonen for full forståelse av spesifikasjonene til hurtigbufferkontrolleren som presenteres her.

- Eventuelle endringer i koden er avhengige av andre moduler. Så endringene bør gjøres på en fornuftig måte. Vær oppmerksom på alle kommentarene og overskriftene jeg har gitt.

- Hvis det av en eller annen grunn ikke blir utledet Block RAM -er for hovedminnet, REDUSER størrelsen på minnet, etterfulgt av endringer i adressebussbredder på tvers av filene og så videre. Slik at det samme minnet kan implementeres enten på LUT eller distribuert RAM. Dette vil spare routing tid og ressurser. Eller gå til den spesifikke FPGA -dokumentasjonen og finn den kompatible koden for Block RAM og rediger koden deretter, og bruk de samme adressebussbreddespesifikasjonene. Samme teknikk for Altera FPGA.

Anbefalt:

Design av en programmerbar avbryterkontroller i VHDL: 4 trinn

Design av en programmerbar interrupt -kontroller i VHDL: Jeg er overveldet over den typen svar jeg får i denne bloggen. Takk gutter for at du besøkte bloggen min og motiverte meg til å dele min kunnskap med deg. Denne gangen skal jeg presentere designet til en annen interessant modul vi ser i alle SOC -er - Interrupt C

Design av I2C Master i VHDL: 5 trinn

Design av I2C Master i VHDL: I denne instruksjonsboken diskuteres det å designe en enkel I2C -master i VHDL. MERK: klikk på hvert bilde for å se hele bildet

Design av SPI Master i VHDL: 6 trinn

Design av SPI Master i VHDL: I denne instruksen skal vi designe en SPI Bus Master fra bunnen av i VHDL

Design av UART i VHDL: 5 trinn

Design av UART i VHDL: UART står for Universal Asynchronous Receiver Transmitter. Det er den mest populære og enkleste seriekommunikasjonsprotokollen. I denne instruksen lærer du hvordan du designer en UART -modul i VHDL

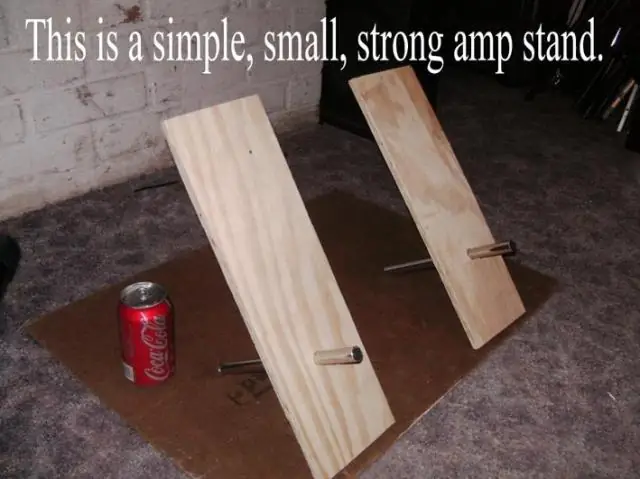

Guitar Amp Tilt Stand - "African Chair" Design - Enkel, liten, sterk, enkel, gratis eller ekte billig: 9 trinn

Guitar Amp Tilt Stand - "African Chair" Design - Enkel, liten, sterk, enkel, gratis eller ekte billig: Guitar Amp Tilt Stand - For lett - enkel, liten, sterk, gratis eller skikkelig billig. For alle forsterkere, til og med store skap med separat hode. Bare lag brett og rør i størrelsen, og du trenger for nesten alt utstyr du ønsker