Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:21.

- Sist endret 2025-01-23 15:02.

I denne instruksjonsboken vil vi beskrive hvordan du implementerer en 8-biters analog-til-digital-omformer (ADC) i SLG46855V som kan registrere laststrøm og grensesnitt med en MCU via I2C. Denne konstruksjonen kan brukes til forskjellige nåværende applikasjoner, for eksempel ammetere, feilsøkingssystemer og drivstoffmålere.

Nedenfor beskrev vi trinnene som trengs for å forstå hvordan løsningen er programmert til å skape ADC nåværende forstand. Men hvis du bare vil få resultatet av programmeringen, kan du laste ned GreenPAK -programvare for å se den allerede fullførte GreenPAK -designfilen. Koble GreenPAK Development Kit til datamaskinen din og klikk på programmet for å opprette ADC nåværende forstand.

Trinn 1: ADC -arkitektur

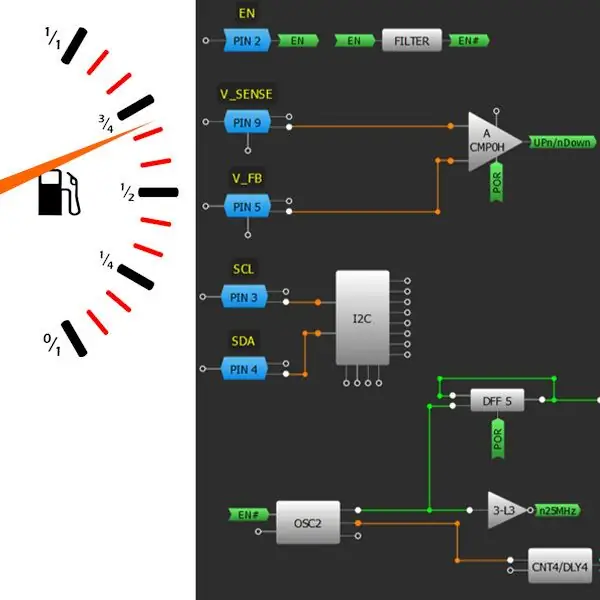

ADC består hovedsakelig av en analog komparator og en Digital-to-Analog Converter (DAC). Komparatoren registrerer inngangsspenningen mot DAC -utgangsspenningen, og kontrollerer deretter om DAC -inngangskoden skal økes eller reduseres, slik at DAC -utgangen konvergerer til inngangsspenningen. Den resulterende DAC -inngangskoden blir den digitale ADC -utgangskoden.

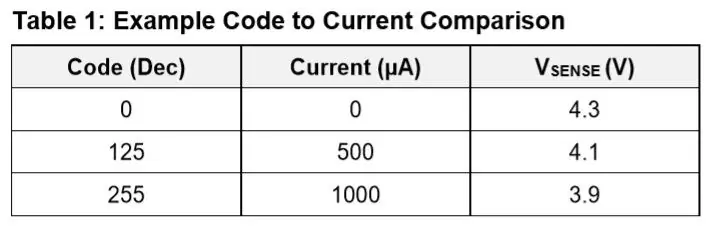

I vår implementering lager vi en DAC ved hjelp av et pulsbreddemodulerings (PWM) kontrollert motstandsnettverk. Vi kan enkelt lage en presis digitalt kontrollert PWM -utgang ved hjelp av GreenPAK. PWM blir når den filtreres vår analoge spenning og fungerer dermed som en effektiv DAC. En tydelig fordel med denne tilnærmingen er at det er enkelt å sette spenningene som tilsvarer nullkode og full skala (tilsvarende forskyvning og forsterkning) ved ganske enkelt å justere motstandsverdier. For eksempel vil en bruker ideelt lese nullkode fra en temperatursensor uten strøm (0 µA) som tilsvarer 4,3 V, og fullskala-kode ved 1000 µA tilsvarende 3,9 V (tabell 1). Dette implementeres enkelt ved ganske enkelt å sette noen få motstandsverdier. Ved å ha ADC -området som samsvarer med sensorintervallet, bruker vi ADC -oppløsningen best.

En designhensyn for denne arkitekturen er at en intern PWM -frekvens må være mye raskere enn ADC -oppdateringshastigheten for å forhindre underdempet oppførsel av kontrollløkken. I det minste bør det være lengre enn ADC -datatellerens klokke delt på 256. I denne designen er ADC -oppdateringsperioden satt til 1,3312 ms.

Trinn 2: Intern krets

Den fleksible ADC er basert på designet som presenteres i Dialog Semiconductor AN-1177. Klokkehastigheten økes fra 1 MHz til 12,5 MHz for å klokke ADC -telleren siden SLG46855 har en 25 MHz klokke tilgjengelig. Dette gir en mye raskere oppdateringshastighet for finere prøveoppløsning. LUT -klokken til ADC -dataklokken endres slik at den vil passere gjennom 12,5 MHz -signalet når PWM DFF er lav.

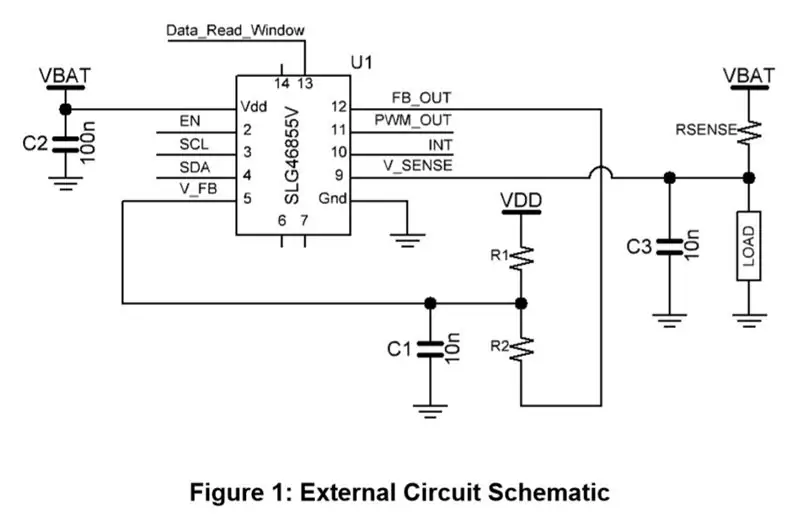

Trinn 3: Ekstern krets

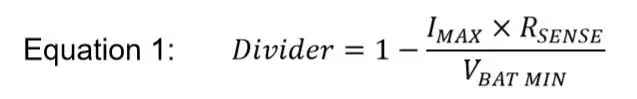

Et eksternt motstands- og kondensatornettverk brukes til å konvertere en PWM til en analog spenning som vist i kretsskjemaet i figur 1. Verdiene beregnes for maksimal oppløsning for maksimal strøm enheten vil føle. For å oppnå denne fleksibiliteten legger vi til motstander R1 og R2 parallelt med VDD og jord. En motstandsdeler deler ned VBAT til den lave siden av spenningsområdet. Delerforholdet for et forventet minimum VBAT kan løses ved hjelp av ligningen 1.

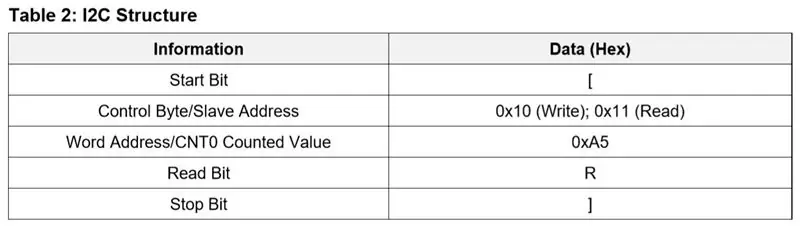

Trinn 4: I2C Les instruksjonene

Tabell 1 beskriver I2C -kommandostrukturen for å lese tilbake dataene som er lagret i CNT0. I2C -kommandoene krever en startbit, kontrollbyte, ordadresse, lesebit og stoppbit.

Et eksempel I2C -kommando for å lese tilbake CNT0 -tellede verdi er skrevet nedenfor:

[0x10 0xA5] [0x11 R]

Den tellede verdien som leses tilbake vil være ADC -kodeverdien. Som et eksempel er en Arduino -kode inkludert i ZIP -filen til dette applikasjonsnotatet på Dialogs nettsted.

Trinn 5: Resultater

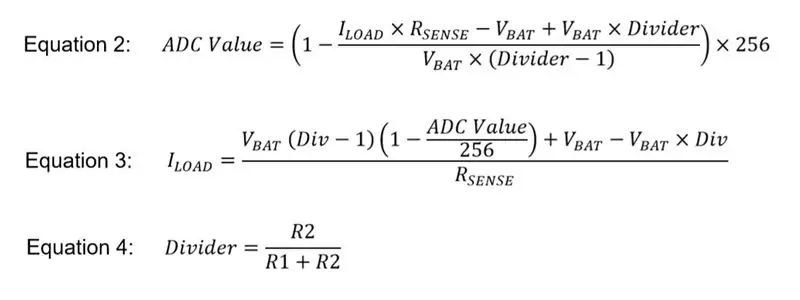

For å teste nøyaktigheten til ADC nåværende sensedesign ble måleverdiene ved en gitt laststrøm og VDD -nivå sammenlignet med en teoretisk verdi. De teoretiske ADC -verdiene ble beregnet med ligningen 2.

ILOAD som korrelerer med en ADC -verdi finnes med ligningen 3.

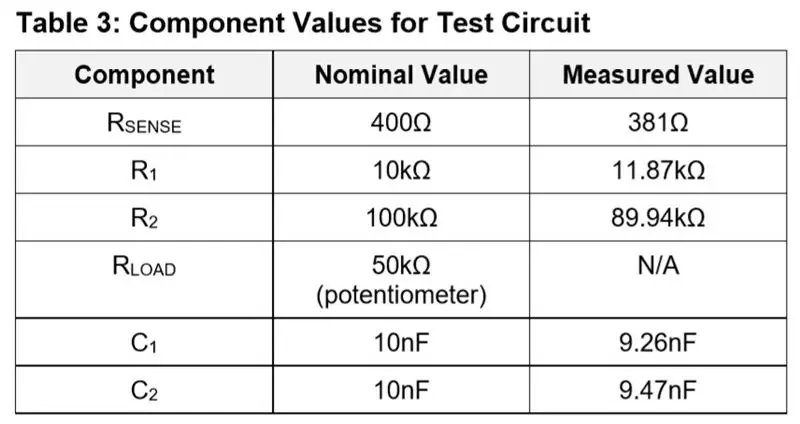

For de følgende resultatene brukte jeg disse komponentverdiene vist i tabell 3.

Oppløsningen av ADC -verdien til ILOAD -konvertering kan beregnes ved å bruke ligning 3 med måleverdiene i tabell 2 og ADC -verdien satt til 1. Med en VBAT på 3,9 V er oppløsningen 4,96 µA/div.

For å optimalisere ADC -strømfølingskretsen til et minimum VDD -nivå på 3,6 V med en maksimal strøm på 1100 µA og en 381 Ω sansemotstand, ville den ideelle divisjonskoeffisienten være 0,884, basert på ligning 1. Med verdiene gitt i tabell 2, har den faktiske skillelinjen en delerkoeffisient på 0,876. Siden dette er litt mindre, vil det muliggjøre et litt større laststrømområde, slik at ADC -verdiene er nær hele området, men ikke overløper. Den faktiske dividerverdien beregnes med ligningen 4.

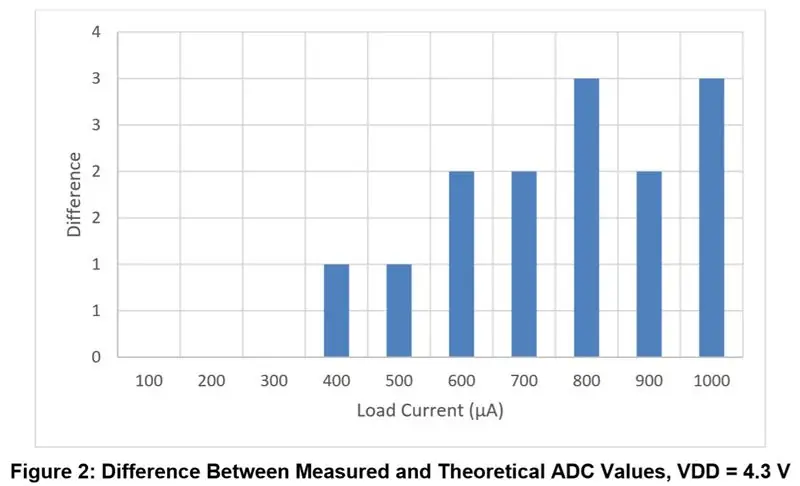

Over (figur 2-6, tabell 4-6) er målingene tatt av kretsen ved tre spenningsnivåer: 4,3 V, 3,9 V og 3,6 V. Hvert nivå viser en graf som viser forskjellen mellom de målte og teoretiske ADC-verdiene. Teoretiske verdier avrundes til nærmeste hele heltall. Det er en oppsummeringsgraf for å sammenligne forskjellene på de tre spenningsnivåene. Etterpå er det en graf som viser korrelasjonen mellom de teoretiske ADC -verdiene og belastningsstrømmen ved de forskjellige spenningsnivåene.

Konklusjon

Enheten ble testet på tre spenningsnivåer: 3,6 V, 3,9 V og 4,3 V. Omfanget av disse spenningene modeller et fullt litiumionbatteri som lades ut til sitt nominelle nivå. Av de tre spenningsnivåene er det observert at enheten vanligvis var mer nøyaktig på 3,9 V for den valgte eksterne kretsen. Forskjellen mellom de målte og teoretiske ADC -verdiene var bare 1 desimalverdi av ved laststrømmer på 700 - 1000 µA. Ved det gitte spenningsområdet var de målte ADC -verdiene 3 desimaler over nominelle forhold i verste fall. Ytterligere justeringer av motstandsdeleren kan gjøres for å optimalisere forskjellige VDD -spenningsnivåer.

Anbefalt:

Hvordan lage 4G LTE Double BiQuade Antenna enkle trinn: 3 trinn

Hvordan lage 4G LTE dobbel BiQuade-antenne til enkle trinn: Mesteparten av tiden jeg møtte, har jeg ikke god signalstyrke til det daglige arbeidet mitt. Så. Jeg søker og prøver forskjellige typer antenner, men fungerer ikke. Etter bortkastet tid fant jeg en antenne som jeg håper å lage og teste, fordi det ikke er byggeprinsipp

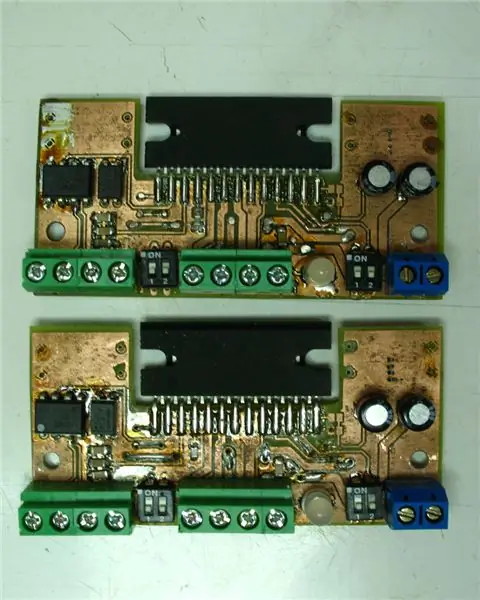

Hvordan lage en HIGH Current Driver for en trinnmotor: 5 trinn

Hvordan lage en HIGH Current Driver for en Stepper Motor: her vil vi se hvordan du lager en stepmotor driver ved hjelp av Toshibas TB6560AHQ kontroller. Dette er en fullverdig kontroller som bare trenger 2 variabler som input, og den gjør alt arbeidet. Siden jeg trengte to av disse, har jeg laget dem begge med

Hvordan lage en Linux -oppstartsdisk (og hvordan du bruker den): 10 trinn

Hvordan lage en Linux Boot Drive (og hvordan du bruker den): Dette er en enkel introduksjon om hvordan du kommer i gang med Linux, spesielt Ubuntu

Hvordan lage et nettsted (en trinn-for-trinn-guide): 4 trinn

Hvordan lage et nettsted (en trinn-for-trinn-guide): I denne veiledningen vil jeg vise deg hvordan de fleste webutviklere bygger nettstedene sine og hvordan du kan unngå dyre nettstedbyggere som ofte er for begrenset til et større nettsted. hjelpe deg med å unngå noen feil som jeg gjorde da jeg begynte

Hvordan lage en besteforeldres kalender & Utklippsbok (selv om du ikke vet hvordan du skal utklippsbok): 8 trinn (med bilder)

Hvordan lage en besteforeldres kalender & Utklippsbok (selv om du ikke vet hvordan du skal utklippsbok): Dette er en veldig økonomisk (og mye verdsatt!) Feriegave til besteforeldre. Jeg laget 5 kalendere i år for mindre enn $ 7 hver. Materialer: 12 flotte bilder av barnet ditt, barn, nieser, nevøer, hunder, katter eller andre slektninger 12 forskjellige stykker