Innholdsfortegnelse:

- Trinn 1: Sette opp et prosjekt i Vivado for Ernie

- Trinn 2: Opprette Ernies PWM i Vivado

- Trinn 3: Lag Ernie's TDOA i Vivado

- Trinn 4: Innpakning og eksport av Ernie

- Trinn 5: Bygge Ernie

- Trinn 6: Ernies første BSP

- Trinn 7: FreeRTOS'ing Ernie

- Trinn 8: Importere Ernies C -kode

- Trinn 9: Debugging Ernie

- Trinn 10: Gjør Ernie autonom

- Trinn 11: Gjør Ernie Cute

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:21.

- Sist endret 2025-01-23 15:02.

Dette er en opplæring om hvordan du bygger Ernie, din autonome lyd etter robot, ved hjelp av et Zybo Board. Den vil dekke hvordan du: oppretter et prosjekt i Vivado, lager PWM-lignende servomotordrivere i FPGA, grensesnitt med to lydsensorer, oppretter en tidsforskjell ved ankomst-IP, bruker freeRTOS og kjører zyboen fra en batteripakke. Dette var vårt siste prosjekt for en Real Time Operating Systems -klasse (CPE 439) på Cal Poly SLO.

Utstyrsliste:

- 1 - ZYBO Zynq 7000 Development Board

- 2 - Parallax Continuous Rotation Servo

- 2 - Lydsensor (SparkFun lyddetektor)

- 1 - 5v litiumion USB -batteripakke (for brett)

- 4 - AA -batterier (for servoer)

- 1 - AA -batteripakke (m/ 4 batterispor)

- 1 - Micro USB -kabel

- 1 - Brødbrett

- mange - mannlige til mannlige ledninger

- 1 - Servo -chassis

Programvarekrav:

- Xilinx Vivado Design Suite 2016.2

- Digilent Adept 2.16.1

Trinn 1: Sette opp et prosjekt i Vivado for Ernie

- En veiviser vil dukke opp

- Klikk Neste

-

Gi prosjektet et nytt navn

- Bruk aldri et prosjektnavn eller en katalogbane som har mellomrom !!!!!

- Dette blir et RTL -prosjekt.

- Vi ønsker ikke å spesifisere kilder

-

Ved å klikke på Neste kommer vi til Delsiden. Vi bruker en ZYNQ XC7Z010-1CLG400C.

- Vivado har ikke Zybo oppført som en av de forhåndsdefinerte tavlene. Velg: “deler”, og søk deretter etter xc7z010clg400-1.

- Hvis du velger feil del ved en feiltakelse, kan du enkelt bytte chips: Verktøy -> Prosjektinnstillinger -> Generelt og klikk på prikkene til høyre for "Project Device"

-

Klikk på Opprett blokkdesign.

Gi den navnet design_1 for nå

- Du vil se en grønn linje som sier Legg til IP, klikk på den.

-

Søk etter Zynq.

- Dobbeltklikk på ZYNQ7 Processing System,

- Denne blokken vil vises i vår blokkdesign.

- Du vil se en grønn linje som sier Run Block Automation, klikk på den.

- Last ned zybo_zynq_def.xml nedenfor.

-

I Vivado klikker du "Importer XPS -innstillinger" og velger "zybo_zynq_def.xml"

Dette befolker Vivado-blokkonfigurasjonen på forhånd med alle Zybo-bordets innebygde eksterne enheter og pin-tildelinger

-

Dobbeltklikk på ZYNQ -blokken.

-

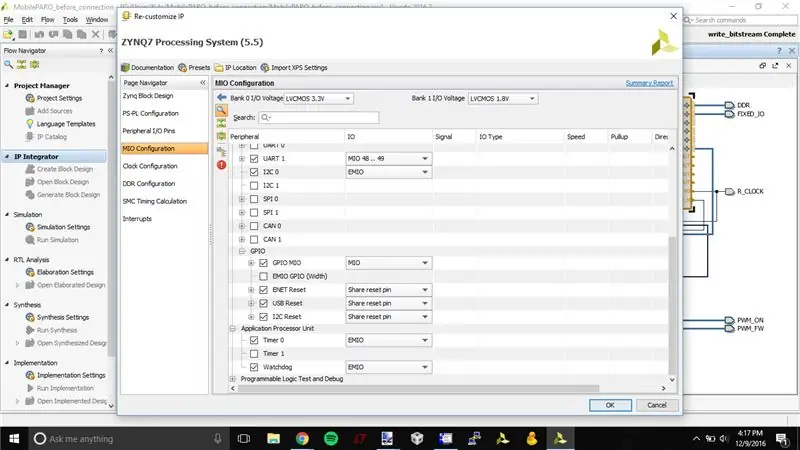

MIO -konfigurasjon

- Aktiver timer 0 (under Application Processor Unit - bilde 1)

- Aktiver Watchdog (under Application Processor Unit- bilde 1)

- Aktiver GPIO-> GPIO MIO (under Application Processor Unit - bilde 2)

- Aktiver GPIO-> ENET Reset (under I/O Peripherals- img 2)

-

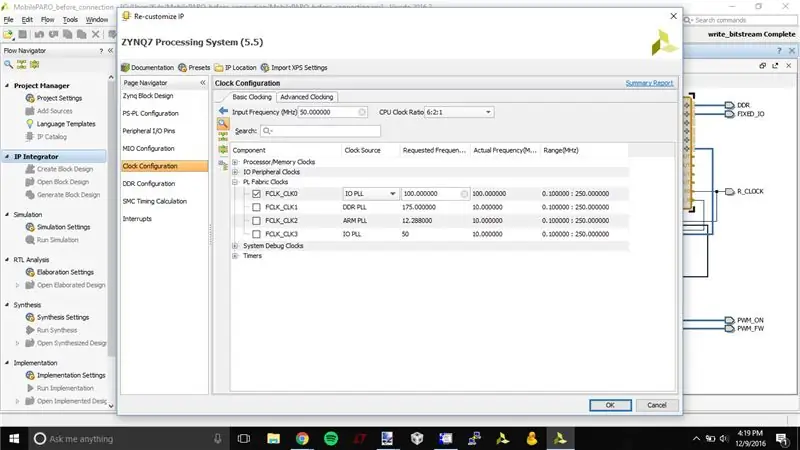

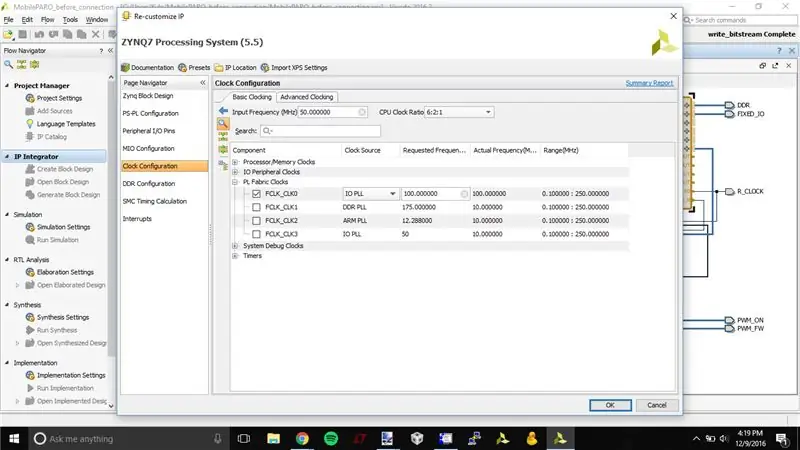

Klokke konfigurasjon

Deaktiver FCLK0 (under PL stoffklokker - bilde 3)

-

- Klikk OK.

-

"Kjør Block Automation" nå.

Det vil være noen spørsmål om signaler, si OK

-

Klikk på "Generer HDL Wrapper".

Vi vil kopiere den genererte innpakningen for å tillate brukerredigeringer

- Klikk OK.

Trinn 2: Opprette Ernies PWM i Vivado

Dette trinnet vil generere en PWM IP med innganger sendt via AXI -biblioteket.

-

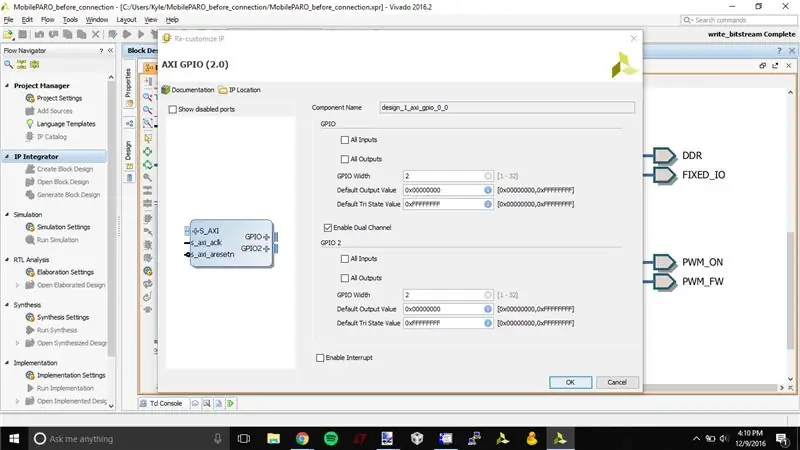

Opprett AXI GPIO-blokk ved å høyreklikke på bakgrunnen og klikke "legg til IP"

skriv "AXI_GPIO" i søkefeltet, og velg denne pakken

-

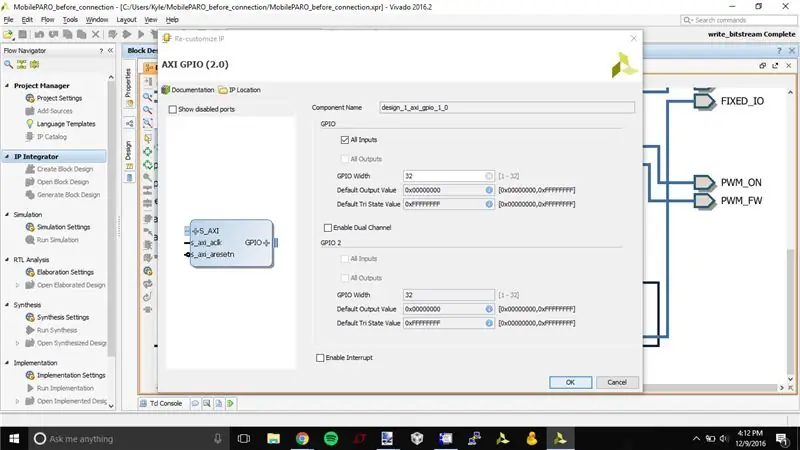

Tilpass IP på nytt ved å dobbeltklikke på den nye axi_gpio_0 blokken

- under GPIO, sett GPIO -bredden til 2. Disse bitene vil være PWM_ON -signalet for å drive hver PWM -modulinstans.

- klikk på "aktiver dobbeltkanal"

- under GPIO 2, sett GPIO -bredden til 2. Disse bitene vil være PWM_FW -signalet for å angi retningen for hver PWM -modulforekomst.

-

Høyreklikk på axi_gpio_0 utgangsporten merket GPIO, og velg "Lag ekstern"

- Klikk på den nye utgangen merket GPIO, og naviger til kategorien "egenskaper" på verktøylinjen til venstre, og endre navnet til PWM_ON

- Klikk på den nye utgangen merket GPIO2, og naviger til kategorien "egenskaper" på venstre verktøylinje, og endre navnet til PWM_FW

-

Velg Kjør tilkoblingsautomatisering i det grønne banneret over blokkdiagrammet.

Hvis du kobler til portene manuelt, er det ikke sikkert at AXI -adresser konfigureres, noe som kan føre til kommunikasjonsproblemer senere

-

I Flow Navigator -ruten velger du prosjektleder -> Legg til kilder for å opprette en ny tilpasset IP -blokk

- velg "legg til eller opprett designkilder", og klikk deretter på neste

- klikk "opprett fil", endre filtype til "SystemVerilog", og skriv "pwm" i filnavnfeltet, klikk deretter OK

- klikk på Fullfør

-

ignorere vinduet Definer modul ved å trykke OK (vi vil overskrive disse senere)

Hvis den spør om du er sikker, klikker du Ja

-

I kategorien Kilder dobbeltklikker du på pwm.sv (ligger i "Designkilder/design_1_wrapper")

Kopier/lim inn hele SystemVerilog -koden fra filen pwm.txt som er vedlagt nedenfor

Trinn 3: Lag Ernie's TDOA i Vivado

Dette trinnet vil generere en TDOA IP hvis utgang kan leses via AXI -biblioteket

-

Opprett AXI GPIO-blokk ved å høyreklikke på bakgrunnen og klikke "legg til IP"

skriv "AXI_GPIO" i søkefeltet, og velg denne pakken

-

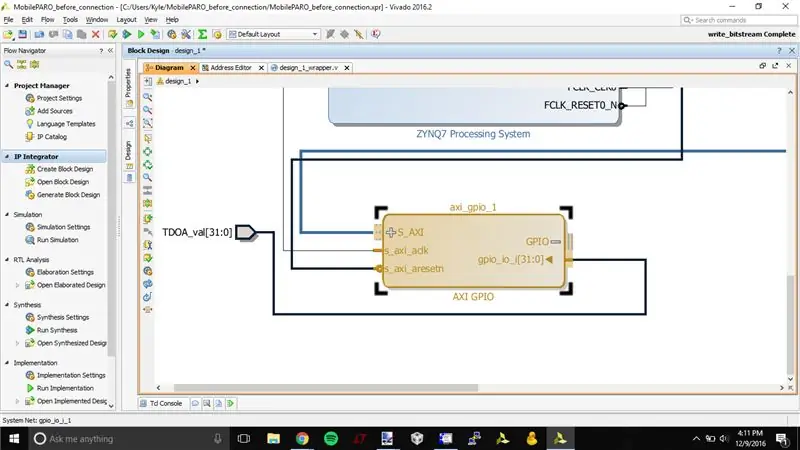

Tilpass IP på nytt ved å dobbeltklikke på den nye axi_gpio_1-blokken

- under GPIO, merker du av for "Alle innganger" og setter GPIO -bredden til 32. Denne bussen vil være tidsforskjellen ved ankomst mellom de to sensorene.

- inne i axi_gpio_1 -blokken klikker du på + ved siden av GPIO -porten for å vise gpio_io_i [31: 0].

-

Høyreklikk på utgangsporten axi_gpio_1 merket gpio_io_i [31: 0], og velg "Lag ekstern"

Klikk på den nye inngangen merket gpio_io_i [31: 0], og naviger til "egenskaper" -fanen på venstre verktøylinje, og endre navnet til TDOA_val

-

Velg Kjør tilkoblingsautomatisering i det grønne banneret over blokkdiagrammet.

Hvis du kobler til portene manuelt, er det ikke sikkert at AXI -adresser konfigureres, noe som kan føre til kommunikasjonsproblemer senere

-

I Flow Navigator -ruten velger du prosjektleder -> Legg til kilder for å opprette en ny tilpasset IP -blokk

- velg "legg til eller opprett designkilder", og klikk deretter på neste

- klikk "opprett fil", endre filtype til "SystemVerilog", og skriv "tdoa" i filnavnfeltet, klikk deretter OK

- klikk på Fullfør

-

ignorere vinduet Definer modul ved å trykke OK (vi vil overskrive disse senere)

Hvis den spør om du er sikker, klikker du Ja

-

I kategorien Kilder dobbeltklikker du på tdoa.sv (ligger i "Designkilder/design_1_wrapper")

Kopier/lim inn hele SystemVerilog -koden fra tdoa.txt -filen som er vedlagt nedenfor

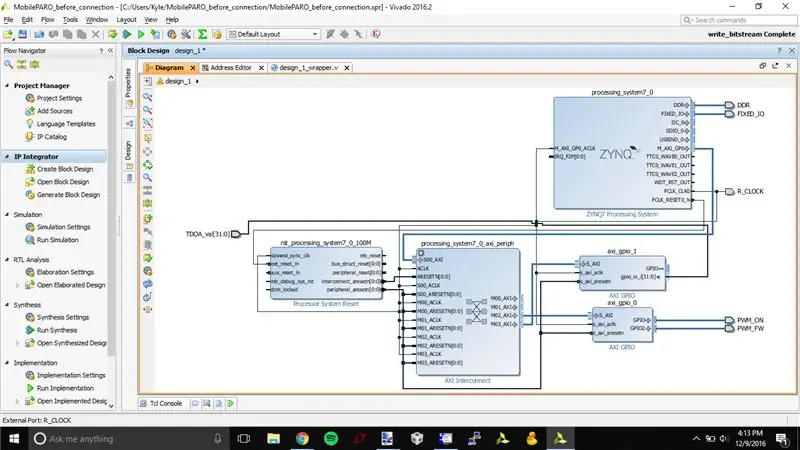

Trinn 4: Innpakning og eksport av Ernie

- Kontroller at blokkdiagrammet ser ut som skjermbildet som er vedlagt

-

I kategorien Kilder, høyreklikker du på design_1.bd og velger "Create HDL Wrapper …"

- Velg "Kopier generert utgang for å tillate brukerredigeringer", og trykk deretter "OK"

- Kopier koden fra design_1_wrapper.txt vedlagt nedenfor, og lim den inn i stedet for den genererte design_1_wrapper.v -koden

- lagre design_1_wrapper.v

-

I kategorien Kilder dobbeltklikker du på filen ZYBO_Master.xdc under Begrensninger/begrensninger1

- Kopier koden fra ZYBO_Master.txt vedlagt nedenfor, og lim den inn i stedet for den eksisterende ZYBO_Master.xdc -koden

-

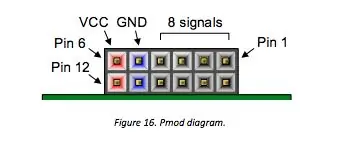

Legg merke til følgende inngangs-/utgangspinner:

- L15: PWM -signal for venstre motor (Pmod JA2 på Zybo)

- L14: PWM -signal for høyre motor (Pmod JA8 på Zybo)

- V12: gateinngang fra lydsensor 1 (Pmod JE1 på Zybo)

- K16: gateinngang fra lydsensor 2 (Pmod JE2 på Zybo)

-

I Flow Navigator -ruten klikker du på "Generer Bitstream" under Program og feilsøking

hvis du tror det er gjort med en gang, er det sannsynligvis ikke det. Seriøst, lag litt te

-

Klikk på File-> Export-> Generate Hardware

Merk av for "Inkluder Bitstream" og trykk OK

- Klikk på File-> Launch SDK

Trinn 5: Bygge Ernie

- Monter servoene på servokabinettet.

-

Følg databladet for servoene:

- koble bakken på servoen til jordpinnene på Zybo's JA Pmod (se vedlagte pinout -bilde)

-

koble strømpinnen til servoene til AA -batteripakken

Vi fant ut at når servoene er koblet til Zybo's Vdd, trekker brettet for mye strøm, noe som får kortet til å tilbakestilles kontinuerlig

- koble inngangssignalpinnene til Zybos passende utgangspinner (venstre: JA2, høyre: JA8)

- Monter lydsensorene foran på chassiset, vendt fremover, og hold dem så tett som mulig

-

bruk lydsensorens tilkoblingsguide for å integrere lydsensorene

- koble bakken og Vdd -pinnene til hver lydsensor til bakken og Vdd -pinnene på Zybo's JE Pmod (se vedlagte pinout -bilde)

- koble den venstre lydsensorens portnål til JE1

- koble den høyre lydsensorens portnål til JE2

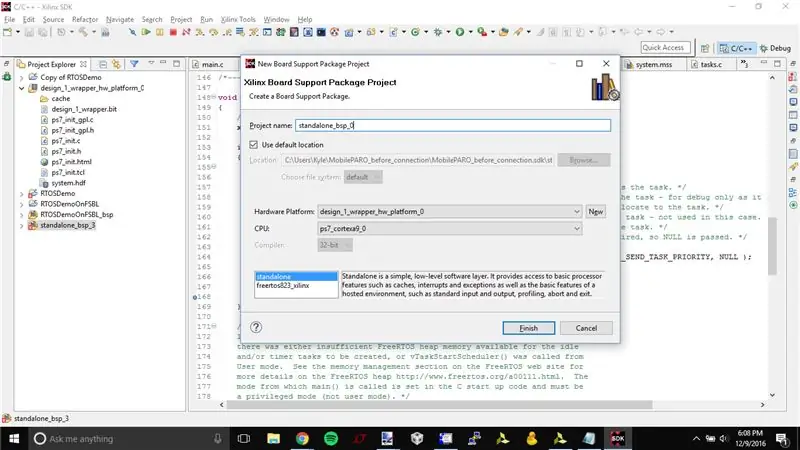

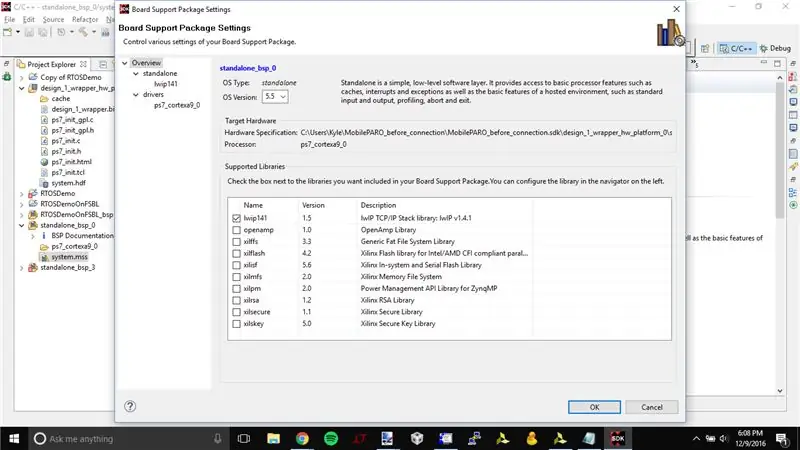

Trinn 6: Ernies første BSP

-

Lag en BSP for å pakke opp plattformen vi nettopp har opprettet.

Du kan få dette gjennom File -> New -> Board Support Package

-

En veiviser vil dukke opp for å hjelpe deg med å lage BSP.

- Vi ønsker å knytte denne BSP med plattformen vår som vi nettopp har opprettet, så

- Maskinvareplattformen bør stå på linje med den vi nettopp har opprettet (se bilde 1)

- CPUen vår vil være _0 CPU.

- Klikk på Fullfør

- Husk å krysse av for lwip141 for inkludering med bsp i vinduet som dukker opp (se bilde 2)

Trinn 7: FreeRTOS'ing Ernie

-

Last ned den siste FreeRTOS -versjonen fra Sourceforge.

Hvis nedlastingen er kjørbar, kan du kjøre den for å pakke ut FreeRTOS -filene i prosjektkatalogen

- Hold SDK -en åpen, og klikk på File -> Import.

- Vi vil klikke Generelt-> Fra et eksisterende arbeidsområde, og så vil vi navigere til der vi lastet ned FreeRTOS.

-

Demoen vår ligger i FreeRTOS/Demo/CORTEX_A9_Zynq_ZC702. Når vi velger denne mappen, bør vi se tre prosjekter dukke opp (vår kode (OS), det er BSP og HW -plattformen).

Importer KUN RTOSDemo til ditt nåværende arbeidsområde

-

På alle "blå" mapprosjekter endrer det refererte BSP

- Høyreklikk og velg "Endre referert BSP."

- Velg BSP du nettopp opprettet for din Zybo

- Koderedigering i Xilinxs SDK Blue -mapper er de faktiske kodeprosjektene.

Trinn 8: Importere Ernies C -kode

- I RTOSDemo/src -katalogen overskriver du den eksisterende main.c -filen med main.c -filen vedlagt her.

- Kopier main_sound.c -filen til RTOSDemo/src -katalogen.

Trinn 9: Debugging Ernie

- Velg Kjør -> Debug Configurations

- I den venstre ruten opprett en ny System Debugger -kjøring

-

I kategorien Måloppsett,

velg “Reset Entire System” slik at både det og ps7_init velges

-

Velg nå kategorien Program.

- Velg "Last ned applikasjon"

- Sett cortexa9_0 -kjernen til "stopp ved programoppføring"

- Klikk på Bruk og feilsøk.

- Kontroller at det ikke er noen feil i feilsøkingsprosessen

- Hold øye med roboten, trykk på Fortsett -knappen til programmet kjører uten å treffe noen bruddpunkter

- Roboten skal nå snu og bevege seg mot høye lyder. Jippi!

Trinn 10: Gjør Ernie autonom

- Når prosjektet er klart til å gå (du kan kjøre uten problemer gjennom feilsøkingsprogrammet) er du klar til å laste det inn i flash -minnet på brettet ditt.

-

Lag det som kalles "first stage boot loader" (FSBL) -prosjektet og inneholder all instruksjonen som brettet ditt trenger for å laste prosjektfilene (bitstrømmen og OS) ved oppstart.

- Velg: File-> New-> Application Project og følgende vindu skal vises.

- Gi det navnet du vil (dvs. "FSBL")

- Sørg for at maskinvareplattformen er den du jobber med

- Trykk på neste (Ikke trykk på Fullfør)

- Velg Zynq FSBL -malen

- Klikk på ferdig.

- Når opprettelsesprosessen er fullført, vil du vite om alt fungerte hvis du ser følgende to nye mapper i vinduet Prosjektutforsker.

-

Lag et oppstartsbilde Nå må du lage oppstartsbildet.

- Høyreklikk på prosjektmappen din (i dette tilfellet heter min "RTOSDemo")

- Klikk "Create Boot image" fra rullegardinmenyen

-

Hvis alt er koblet riktig, vil prosjektet vite hvilke filer det trenger, og det følgende vinduet vil se ut som du ser nedenfor (nøkkelen er at du har 3 partisjoner under Boot image -delen, bootloaderen, bitfilen og prosjektene.elf -filen din).

Hvis dette ikke er tilfelle, er det muligens noe galt med prosjektlinken din. Forsikre deg om at prosjektmappene er knyttet til sine respektive BSP -er

- Klikk på "Lag bilde" -knappen

-

Det siste trinnet å utføre i programvare er å nå blinke det tidligere opprettede bildet ditt i minnet på brettet

- Velg fra SDKs hovedverktøylinje, velg Xilinx Tools-> Program Flash Memory

- Forsikre deg om at riktig maskinvareplattform er valgt og at bildefilbanen peker riktig på. BIN -filen som ble opprettet i forrige trinn.

- Velg "qspi singel" fra Flash -typen

- Merk av for “Bekreft etter blits” for å sikre integriteten, men det er ikke nødvendig

- Konfigurer tavlen Til slutt må du forsikre deg om at jumperen for programmeringsmodus for brettene (JP5) er riktig angitt for å velge å starte fra qspi (som inneholder det du nettopp blinket) når BootROM kjøres.

- Slå nå av og på enheten og forsikre deg om at "Logic Configuration Done LED" (LED 10) lyser grønt.

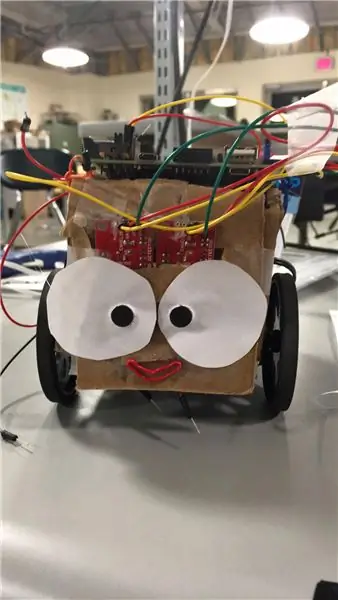

Trinn 11: Gjør Ernie Cute

- Pels

- Mye pels

- Store øyne!

- … topphatt

Anbefalt:

Hvordan lage 4G LTE Double BiQuade Antenna enkle trinn: 3 trinn

Hvordan lage 4G LTE dobbel BiQuade-antenne til enkle trinn: Mesteparten av tiden jeg møtte, har jeg ikke god signalstyrke til det daglige arbeidet mitt. Så. Jeg søker og prøver forskjellige typer antenner, men fungerer ikke. Etter bortkastet tid fant jeg en antenne som jeg håper å lage og teste, fordi det ikke er byggeprinsipp

Hvordan lage en Linux -oppstartsdisk (og hvordan du bruker den): 10 trinn

Hvordan lage en Linux Boot Drive (og hvordan du bruker den): Dette er en enkel introduksjon om hvordan du kommer i gang med Linux, spesielt Ubuntu

Hvordan lage et nettsted (en trinn-for-trinn-guide): 4 trinn

Hvordan lage et nettsted (en trinn-for-trinn-guide): I denne veiledningen vil jeg vise deg hvordan de fleste webutviklere bygger nettstedene sine og hvordan du kan unngå dyre nettstedbyggere som ofte er for begrenset til et større nettsted. hjelpe deg med å unngå noen feil som jeg gjorde da jeg begynte

Hvordan lage en delt skjermvideo med fire trinn: 4 trinn (med bilder)

Hvordan lage en delt skjermvideo med fire trinn: Vi ser ofte en samme person vise i en scene to ganger i et TV -spill. Og så vidt vi vet har ikke skuespilleren en tvillingbror. Vi har også sett at to sangvideoer blir satt på en skjerm for å sammenligne sangferdighetene sine. Dette er kraften til spl

Hvordan lage en besteforeldres kalender & Utklippsbok (selv om du ikke vet hvordan du skal utklippsbok): 8 trinn (med bilder)

Hvordan lage en besteforeldres kalender & Utklippsbok (selv om du ikke vet hvordan du skal utklippsbok): Dette er en veldig økonomisk (og mye verdsatt!) Feriegave til besteforeldre. Jeg laget 5 kalendere i år for mindre enn $ 7 hver. Materialer: 12 flotte bilder av barnet ditt, barn, nieser, nevøer, hunder, katter eller andre slektninger 12 forskjellige stykker