Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:21.

- Sist endret 2025-01-23 15:02.

I denne opplæringen skal vi bruke FPGA til å kontrollere ekstern LED -krets. Vi skal gjennomføre følgende oppgaver

(A) Bruk trykknappene på FPGA Cyclone IV DuePrologic for å kontrollere LED.

(B) Blitslys på og av med jevne mellomrom

Videodemo

Lab-meny: https://roywchpi.blogspot.com 2020/06/10-fpga-dueprologic-push-button-led.html

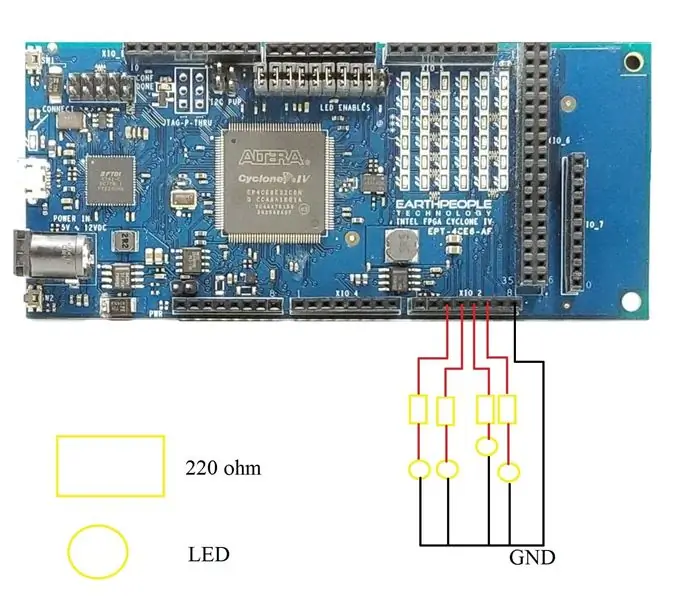

Trinn 1: Bygg elektronisk krets

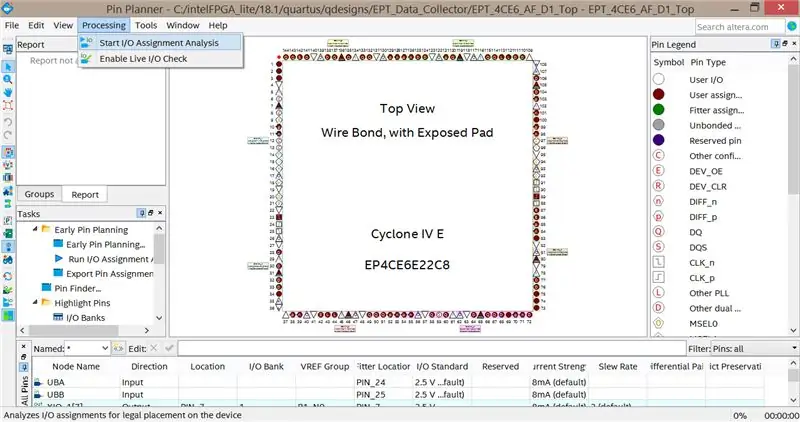

Trinn 2: Sjekk Pin -planleggeren og rediger Verilog -koden

Trinn 3: Rediger Verilog -koden

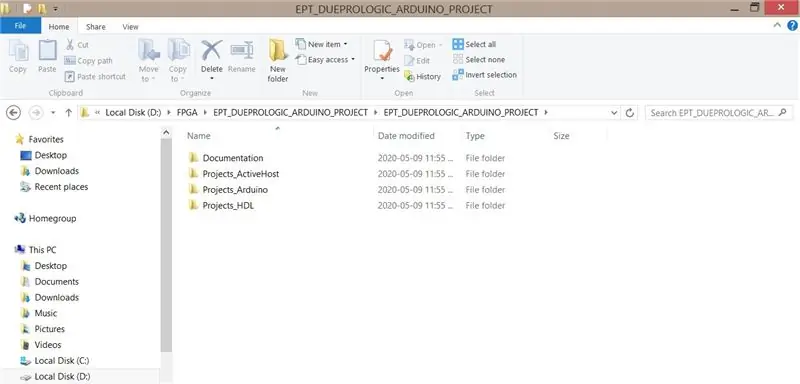

Når du kjøper FPGA DueProLogic, bør du motta en DVD. Etter at du har åpnet "Projects_HDL", bør du se den originale kodefilen

Legg til den uthevede koden. Den registrerer I/O -portene og tildeler nummer til portene.

utgangskabel [7: 0] XIO_1, // XIO-D2-D9

utgangskabel [5: 0] XIO_2, // XIO-D10-D12

utgangskabel [5: 0] XIO_3, // XIO-D22-D29

inngangskabel [5: 0] XIO_4, // XIO-D30-D37

inngangskabel [5: 0] XIO_5, // XIO-D38-D45

utgangskabel [4: 0] XIO_6_OUT, // XIO-D46-D53

inngangskabel [31: 5] XIO_6, // XIO-D46-D53

utgangskabel [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

inngangskabel UBA, // Trykknappbrytere

inngangskabel UBB // Trykknappbrytere

tilordne XIO_1 [3] = start_stop_cntrl;

tilordne XIO_2 [1] = start_blinky; // LED blits LED av og på

tilordne XIO_2 [2] = 1'b1; // utgang HØY

tilordne XIO_2 [3] = ~ UBA; // Trykknapp A

tilordne XIO_2 [4] = UBB; // Trykknapp B

tilordne c_enable = XIO_5 [2];

tilordne LEDExt = XIO_5 [5];

Deretter må vi stille en tidsforsinkelse. Kommenter den originale timer -koden og skriv en ny timer -funksjon

//-----------------------------------------------

// LED Blinkende start

//-----------------------------------------------

/*

alltid @(posedge CLK_66 eller negedge RST)

begynne

hvis (! RST)

start_blinky <= 1'b0;

ellers

begynne

hvis (kontrollregister [7: 4]> 0)

start_blinky <= 1'b1;

ellers

start_blinky <= 1'b0;

slutt

slutt

*/

reg [31: 0] eks;

første start

eks <= 32'b0;

start_blinky <= 1'b0;

slutt

alltid @(posedge CLK_66)

begynne

eks <= eks + 1'b1;

hvis (eks> 100000000) // blits på/av ~ 1,6 sekunder, klokke 66MHz

begynne

start_blinky <=! start_blinky;

eks <= 32'b0;

slutt

slutt

//-----------------------------------------------

// LED Delay Timer Counter

//-----------------------------------------------

/*

alltid @(posedge CLK_66 eller negedge RST)

begynne

hvis (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

ellers

begynne

hvis (oppgi [SELECT_MODE])

led_delay_counter <= timer_value;

annet hvis (oppgi [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

slutt

slutt*/

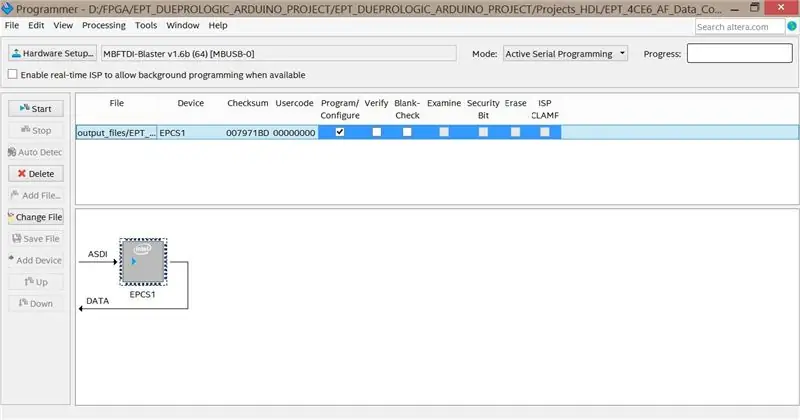

Trinn 4: Kompiler Verilog -kode

Trykk på "Start kompilering" i Quartus, ingen feilmelding skal genereres.

Hvis du får feilmelding om flere pins. Gå til Oppgaver -> Enhet -> Enhets- og pinnealternativer -> Pinner med to formål -> endre verdien på den riktige pinnen til "Bruk som vanlig I/O".

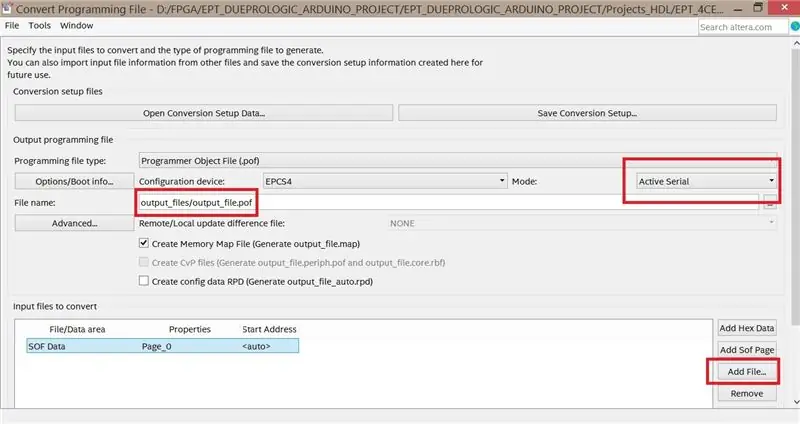

Etter kompilering bør du få pof -utdatafilen direkte. Hvis programvaren din ikke er oppdatert, kan det hende du bare får sof-fil. Når det skjer, klikker du "File" i Quartus -> "konverter programmeringsfiler". Endre innstillingene som er markert med røde bokser.

Trinn 5: La oss prøve det

Tross alt burde det fungere !!! Den gule LED -en er alltid på. Den røde LED -en blinker. Den blå lysdioden slås av hvis du trykker på knapp B. Den grønne lysdioden lyser hvis du trykker på knapp A

Anbefalt:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: 5 trinn

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: Til tross for at FPGA DueProLogic er offisielt designet for Arduino, skal vi gjøre FPGA og Raspberry Pi 4B kommuniserbare. Tre oppgaver implementeres i denne opplæringen: (A) Trykk samtidig på de to trykknappene på FPGA for å snu vinkelen på

FPGA Cyclone IV DueProLogic Controls Servomotor: 4 trinn

FPGA Cyclone IV DueProLogic Controls Servomotor: I denne opplæringen skal vi skrive Verilog -kode for å kontrollere servomotor. Servoen SG-90 er produsert av Waveshare. Når du kjøper servomotoren, kan du motta et datablad som viser driftsspenningen, maksimalt dreiemoment og den foreslåtte Pu

Arduino Cyclone Game: 5 trinn (med bilder)

Arduino Cyclone Game: Jeg har aldri spilt det virkelige syklonspillet, men jeg liker tanken på å spille med reaksjonstiden min. Jeg designet et miniatyrisert spill. Den består av 32 lysdioder som danner en sirkel, lysdiodene lyser en etter en som en leddjager. Målet er å trykke på en rumpe

Cyclone (Arduino LED Game): 6 trinn (med bilder)

Cyclone (Arduino LED Game): I denne opplæringen vil jeg lære deg hvordan du lager et LED -spill med veldig lite kode eller erfaring! Jeg hadde denne ideen en stund, og endelig kom jeg til å lage den. Det er et morsomt spill som minner oss alle om arkadespillene. Det finnes andre opplæringsprogrammer for

Cyclone LED Arcade Game: 4 trinn

Cyclone LED Arcade Game: Hensikten med dette prosjektet var å lage et enkelt spill ved hjelp av en Arduino som ville være interaktiv og underholdende for barn. Jeg husker at Cyclone arkadespill var et av mine favoritt arkadespill da jeg var yngre, så jeg bestemte meg for å replikere det. T