Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:23.

- Sist endret 2025-01-23 15:02.

Har du noen gang forestilt deg hvordan tastaturet tar input og hvordan dataene lagres! Dette prosjektet er en mindre versjon av datainføring og lagring. En utførlig forklaring på hvordan signalet fra tastene, klokken påvirker minneelementene (flip -flops).

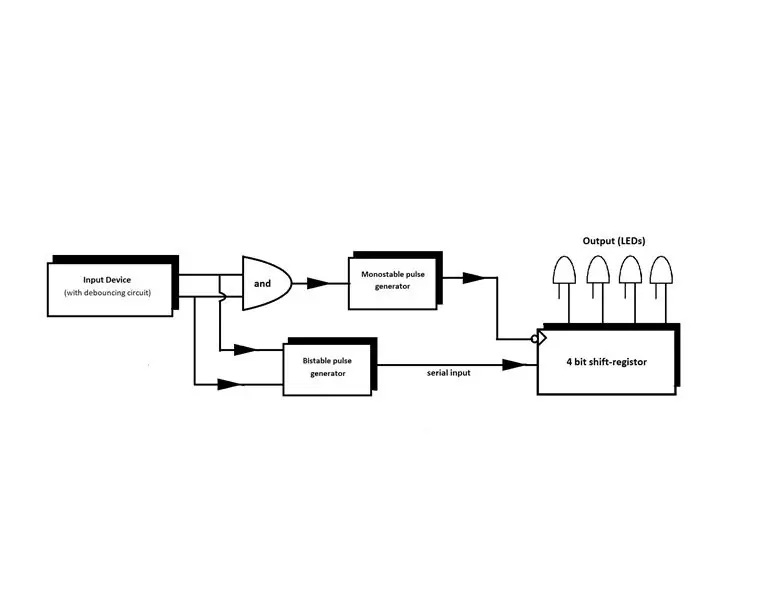

Trinn 1: Blokkdiagram

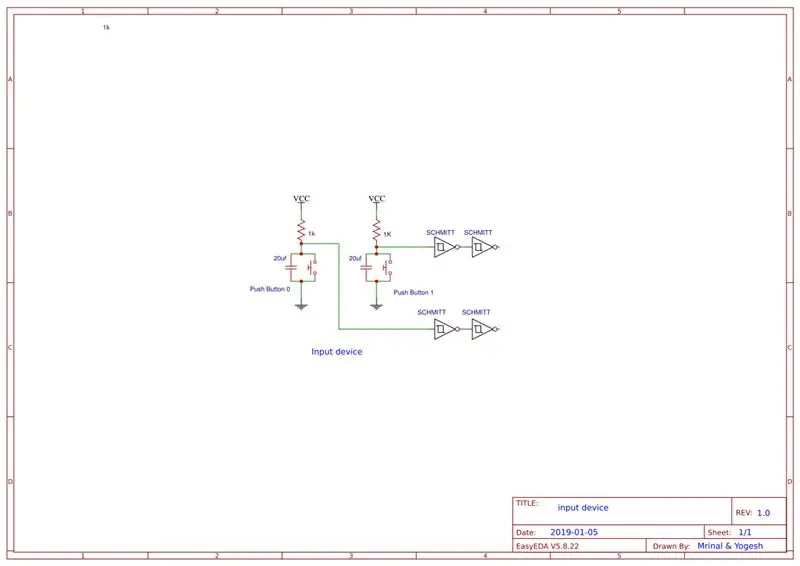

1. Inndataenhet

Asa binær 4 -bits inndataenhet er det bare 2 trykknapper (en for å registrere 1 (høy) og en for 0 (lav) med et støyfilter som kreves for å generere inngangssignalet. Utgangssignalet som genereres er en nullpuls (når tasten trykkes det alltid det høye signalet til lavt).

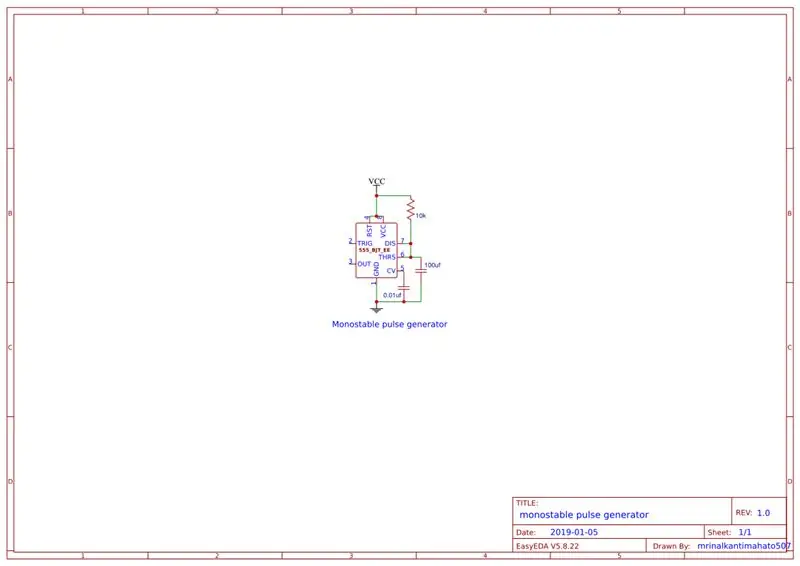

2. Monostabil pulsgenerator

Inngangssignalene mates deretter inn i den monostabile pulsgeneratoren for å generere en puls som har en fast høy tidsvarighet, den utløses av den lille inngangspulsen. Denne monostabile pulsen brukes som en klokkeinngang til skiftregisteret.

3. Bi-stabil pulsgenerator

Denne pulsen drives også av inngangssignallinjene. Når den ene (høye) tasten trykkes inn, settes dette signalet og tilbakestilles når lavtasten trykkes. Signalet mates som venstre seriell inngang til skiftregisteret.

4. Skiftregister

4-bits skiftregister bruker 4 flip-flops for å lagre data. Det tar en seriell inngang med en klokke for å lagre dataene enten fra venstre til høyre eller høyre til venstre. I dette prosjektet kommer de serielle dataene vi bruker fra den bi-stabile pulsgeneratoren og klokkesignalet fra en monostabil pulsgenerator.

5. Utgang

Lysdiodene indikerer utgangen.

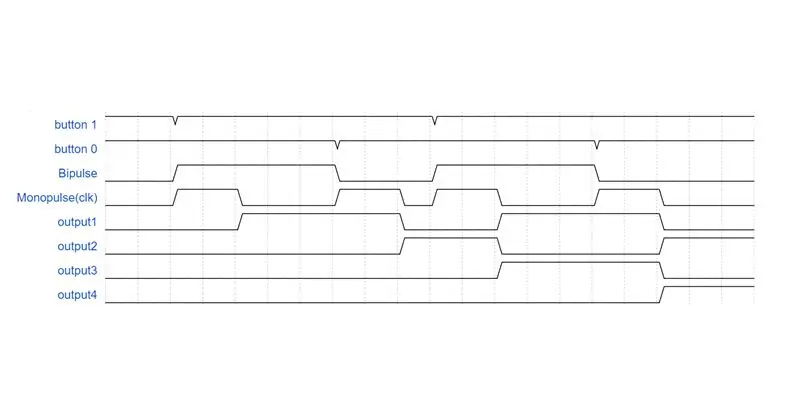

Trinn 2: Timing Diagram

Et eksempel på tidsdiagram som tar en inngang 0101. Inngangspulsen fra knapp 1 og knapp 2 har en veldig liten "lav tid", det er grunnen til at den vises som en økning i timediagrammet.

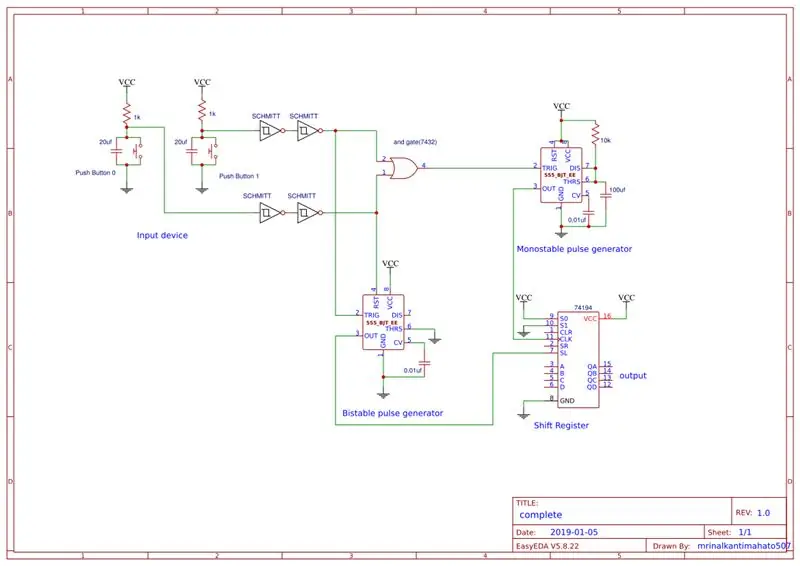

Trinn 3: Kretsdiagram

Høy tid for den monostabile pulsen kan endres ved å endre RC -verdien (motstand og kapasitansverdi). Høy tid er gitt med t = 1,1*RC. Den høye tiden har en nedre grense som avhenger av denunouncing -bryteren som brukes, grensen er generelt 10-20 ms. Høy tid i denne kretsdesignen er 1s (10k omh*100uf).

Dette ved å redusere denne gangen hastigheten på enheten økes.

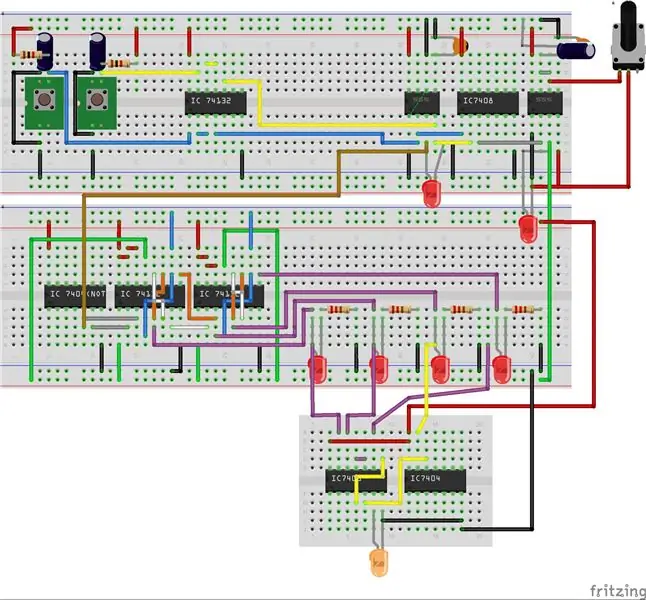

Trinn 4: Fritzing -design med BOM -filer

Last ned fritzing -filen for å tilpasse designet og lage ditt eget design.

Den nødvendige komponentlisten er i BOM -filen.

Anbefalt:

Raspberry PI 3 - Aktiver seriell kommunikasjon til TtyAMA0 til BCM GPIO 14 og GPIO 15: 9 trinn

Raspberry PI 3 - Aktiver seriell kommunikasjon til TtyAMA0 til BCM GPIO 14 og GPIO 15: Jeg hadde nylig interesse for å aktivere UART0 på min Raspberry Pi (3b) slik at jeg kunne koble den direkte til en RS -232 signalnivåenhet ved hjelp av en standard 9 -nål d-sub-kontakt uten å måtte gå gjennom en USB til RS-232 adapter. En del av min interesse

OrangeBOX: OrangePI -basert sikker lagringsenhet for sikkerhetskopiering: 5 trinn

OrangeBOX: OrangePI-basert sikker lagringsenhet for sikkerhetskopiering: OrangeBOX er en alt-i-ett ekstern lagringsboks for eksterne servere. Serveren din kan bli infisert, ødelagt, slettet og alle dataene dine er fremdeles sikre på OrangeBOX, og hvem vil ikke like et umulig oppdrag som sikkerhetskopieringsenhet det du bare planlegger

Slik formaterer du en ekstern lagringsenhet ved hjelp av Mac OS X: 10 trinn

Hvordan reformatere en ekstern lagringsenhet ved hjelp av Mac OS X: Selge en gammel USB? Eller datamaskin? Bruk denne enkle trinnvise veiledningen for å formatere den eksterne lagringsenheten på din Mac. Fordelene med denne omformateringen av en harddisk er delsikkerhet, dels bekvemmelighet og dels gjenbruk. Dette vil hjelpe til med å

Passiv 3 -inngangs stereomikser: 4 trinn

Passiv 3 -inngangs stereomikser: Denne instruksjonsfilen viser deg hvordan du bygger en enkel stereomikser. Selv om denne boksen bare har 3 stereoinnganger, kan du enkelt oppgradere den til så mange du trenger! Jeg ønsket å bygge denne boksen for å koble flere lydinnganger til en enkelt utgang. Jeg er

USB -hub -lagringsenhet i disketter !: 5 trinn

USB Hub -lagringsenhet i disketter !: Har du alle lyst til å ha en portallager som er veldig lett, har minst 8 GB lagringsplass, trenger du ikke bry deg om den faller ned, du kan ha den overalt og du kan bære den faktisk alt operativsystemet med noen Office -applikasjoner og alle disse programmene