Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:22.

- Sist endret 2025-01-23 15:02.

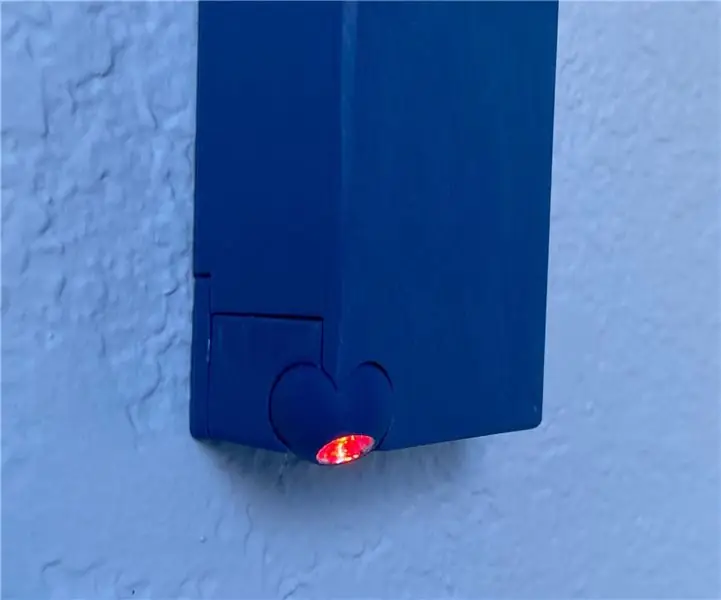

Målet vårt med dette prosjektet var å skape noe som ville spare lokalsamfunn for energi og økonomiske ressurser. Bevegelsesaktiverte gatelys ville gjøre begge disse tingene. Over hele landet blir energien bortkastet på gatelys som belyser gater som er tomme. Gatesystemet vårt sørger for at lysene bare er på når det trengs, og sparer samfunn for utallige dollar. Ved hjelp av bevegelsessensorer tenner systemet bare lys når biler er til stede. Også for fotgjengernes sikkerhet implementerte vi en overstyringsknapp som tenner alle lysene på gaten. Følgende trinn vil lede deg gjennom hvordan vi designet og bygde vår nedskalerte modell av prosjektet ved hjelp av Vivado og et Basys 3 -bord.

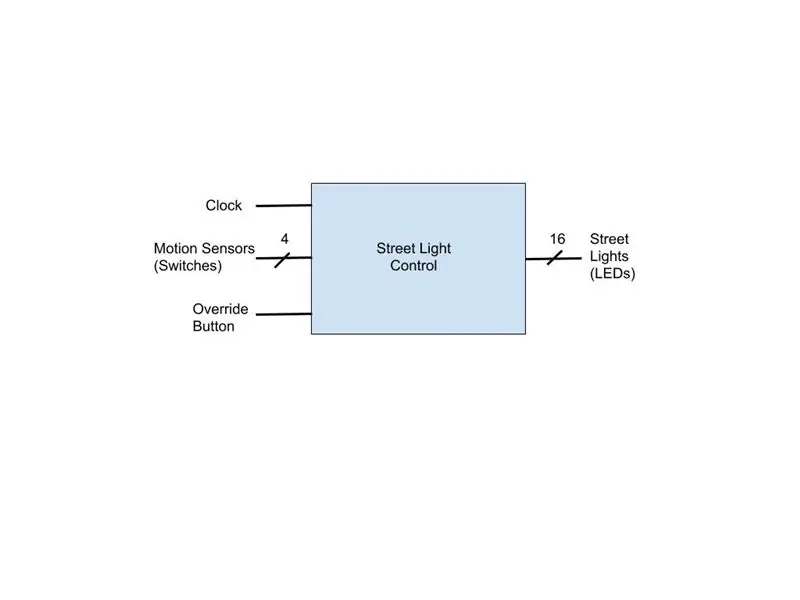

Trinn 1: System Black Box

Vi begynte dette prosjektet med å tegne et enkelt svart boks -diagram. Et svart boksdiagram viser ganske enkelt innganger og utganger systemet vårt krever for å fullføre alle nødvendige prosesser. Vi prøvde å holde designet så enkelt og grunnleggende som mulig. Våre tre systeminnganger inkluderte en buss med bevegelsessensorer (4 for vår nedskalerte modell), en overstyringsknapp for fotgjengere og en klokkeinngang. På den andre siden er vår eneste utgang en buss med LED -lys som representerer våre gatelys. For denne modellen brukte vi et scenario med 16 gatelys rett og slett fordi det er det maksimale antallet innebygde LED -utganger på Basys 3 -kortet. Til slutt, ved hjelp av dette diagrammet, var vi i stand til å lage vårt Vivado -prosjekt, kilde- og begrensningsfiler med passende innganger og utganger.

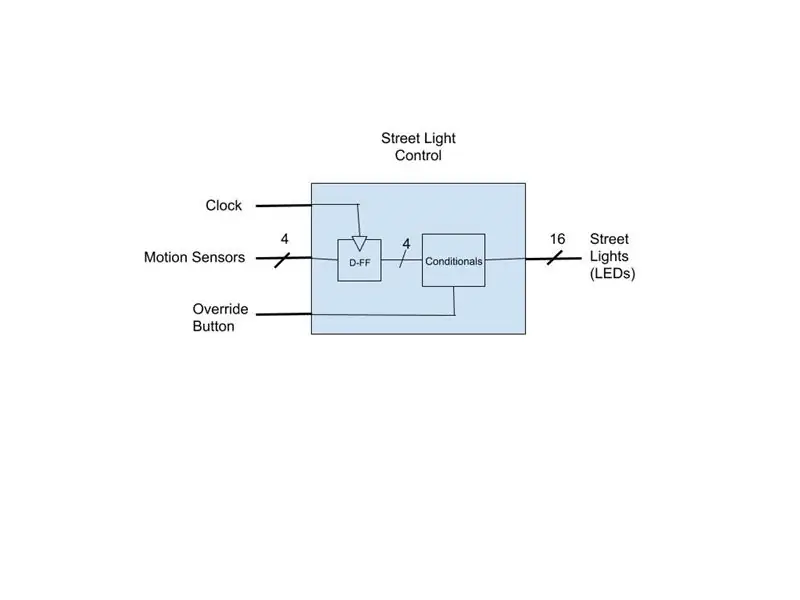

Trinn 2: Komponenter

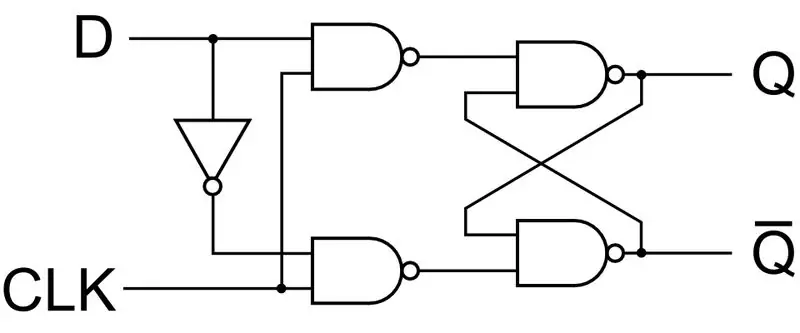

I dette trinnet dykker vi dypere for å undersøke komponentene i vårt black box -diagram. Vår første komponent er en VHDL-kildefil som inneholder D-flip-flops. D flip-flops tar ganske enkelt det signalet som sendes til dem fra sensorene på klokkens stigende kant, og låser dataene inn til neste stigende kant. Dette holder våre følsomme bevegelsessensorer fra å forårsake at utgangs -LED -ene flimrer. Vi legger også en enkelt D-vippe på knappens inngangssignal for å holde lysdiodene på i omtrent 5-7 sekunder etter at knappen er trykket. Vi kjørte også dette gjennom en klokkeskille.

enhet clk_div2 er Port (clk: in std_logic; sclk: out std_logic); avslutte clk_div2;

arkitektur my_clk_div av clk_div2 er

konstant max_count: heltall: = (300000000); signal tmp_clk: std_logic: = '0'; start my_div: prosess (clk, tmp_clk) variabel div_cnt: heltall: = 0; start if (rising_edge (clk)) så if (div_cnt = MAX_COUNT) deretter tmp_clk <= ikke tmp_clk; div_cnt: = 0; annet div_cnt: = div_cnt + 1; slutt om; slutt om; sclk <= tmp_clk; avslutte prosessen my_div; avslutte my_clk_div;

Vår siste komponent i dette diagrammet er en atferdsmessig VHDL -kildefil som inneholder betingelser for utgangene basert på konfigurasjonen av inngangssignaler.

Trinn 3: D Flip-flops

De fire vippene som er festet til inngangssignalene er avgjørende for funksjonaliteten til systemet vårt. Som sagt tidligere, med følsomme bevegelsessensorer og en overstyringsknapp, bruker vippene låser for å bare sende ut inngangssignalet på klokkens stigende kant. Denne sekvensielle logikken betyr at gatelysene våre kan forbli på i en bestemt periode etter å ha blitt utløst av en rask bevegelse. Kodingen for en D-Flip Flop er ganske enkel:

beginprocess (CLK) begynner hvis rising_edge (CLK) deretter Q <= D; slutt om; avslutte prosessen;

Det hele kan samles til en enkelt if -setning. Når vi hadde dette stykket, opprettet vi en strukturell VHDL-kildefil som inneholder alle fire av våre nødvendige flip-flops:

begynne DFF0: DFF -portkart (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF -portkart (CLK => CLK, D => D (1), Q => Q (1)); DFF2: DFF -portkart (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF -portkart (CLK => CLK, D => D (3), Q => Q (3));

slutt Behavioral;

Dette bidrar til å beholde vår hovedstrukturfil der vi samler alle systemkomponenter mye mer rene og organiserte.

Trinn 4: Betingelser

For å beholde koden vår kompakt og effektiv skrev vi alle betingelsene våre i en enkelt sakssak. For vår nedskalerte modell hadde vi 16 mulige LED -utgangskonfigurasjoner ettersom hver bevegelsessensor er ansvarlig for en gruppe på 4 lysdioder.:

tilfelle NMS er når "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; slutt saken;

Trinn 5: Begrensninger

For å angi inngang og utgang på riktig måte ved hjelp av Vivado, må du implementere en begrensningsfil som angir alle porter, knapper, lysdioder og klokker som brukes.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports_ LED] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_ LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11] }33] [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] [prop_PACK] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

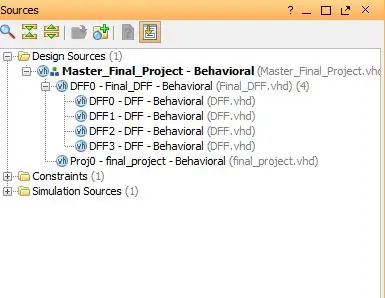

Trinn 6: Hovedkildefil

I denne hovedfilen samler vi alle komponentkildefilene som er nevnt tidligere. Denne filen fungerer som strukturell kode som samler de forskjellige komponentene.

enhet Master_Final_Project er Port (BTN: i STD_LOGIC; CLK: i STD_LOGIC; MS: i STD_LOGIC_VECTOR (3 ned til 0); LED: ut STD_LOGIC_VECTOR (15 ned til 0)); avslutte Master_Final_Project;

arkitektur Behavioral of Master_Final_Project is

komponent final_project er Port (--CLK: i STD_LOGIC; NMS: i STD_LOGIC_VECTOR (3 ned til 0); BTN: i STD_LOGIC; --sw: i STD_LOGIC_Vector (1 ned til 0); LED: ut STD_LOGIC_VECTOR (15 ned til 0)); sluttkomponent;

komponent Final_DFF er

Port (CLK: i STD_LOGIC; D: i STD_LOGIC_Vector (3 ned til 0); Q: ut STD_LOGIC_Vector (3 ned til 0)); sluttkomponent;

signal DFF02proj30: STD_LOGIC;

signal DFF12proj74: STD_LOGIC; signal DFF22proj118: STD_LOGIC; signal DFF32proj1512: STD_LOGIC;

begynne

DFF0: Final_DFF portkart (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: final_project port map (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); slutt Behavioral;

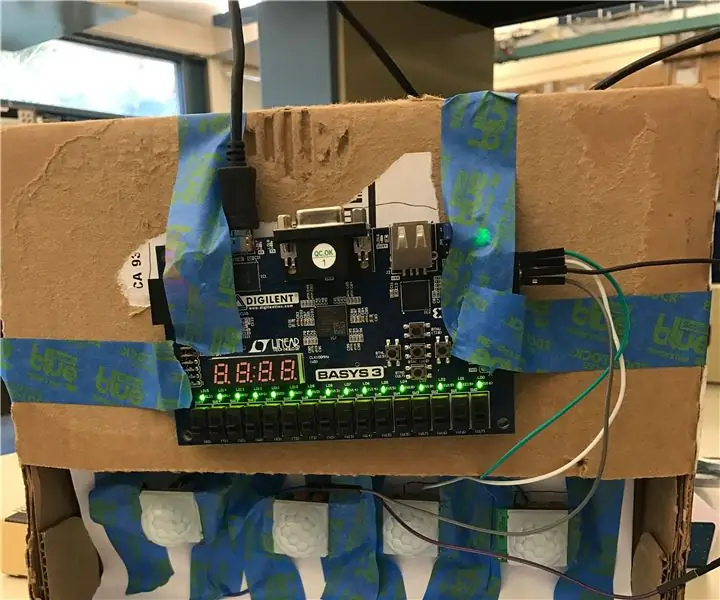

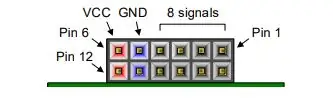

Trinn 7: Montering

Maskinvaremontasjen for dette prosjektet er minimal. De eneste nødvendige brikkene er som følger:

1. Basys 3 bord (1)

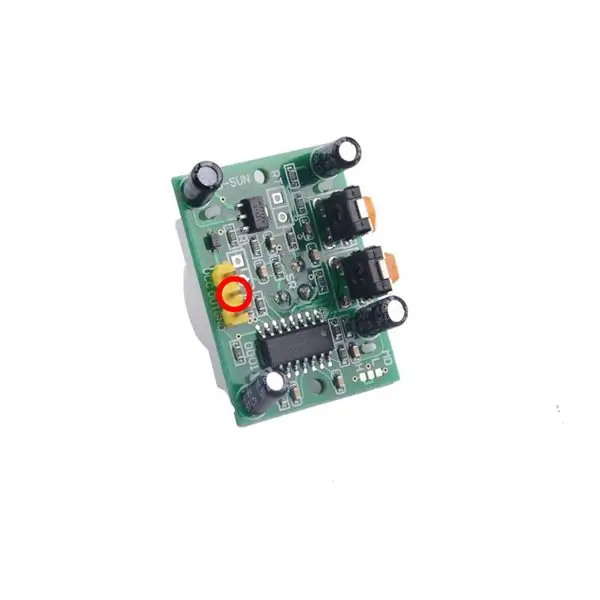

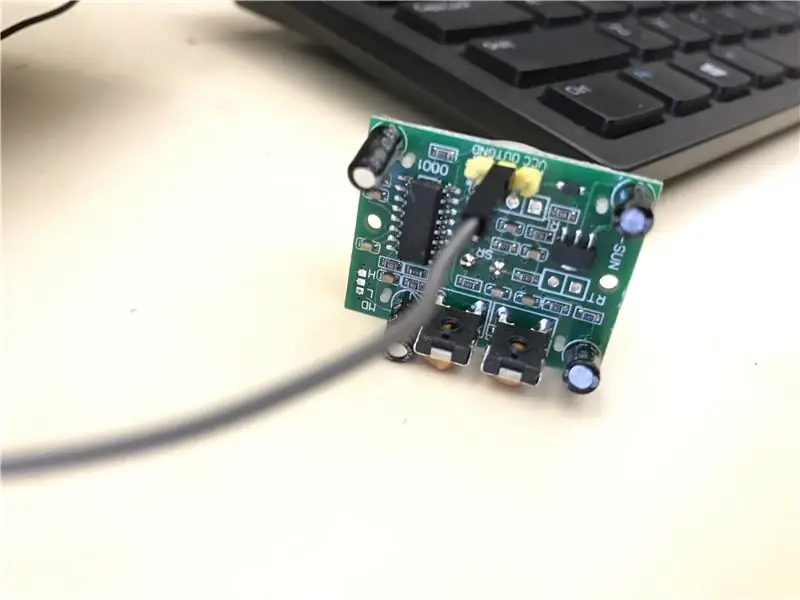

2. Billige bevegelsessensorer som du finner på Amazon her. (4)

3. Mann-til-kvinne leder (4)

Montering:

1. Koble 4 hannledninger til PMod-topptekst JB-porter 1-4 (se figur).

2. Koble hunnendene til hver bevegelsessensors utgangspinne.

Trinn 8: Laster inn programmet

Nå er vi klare til å laste inn VHDL -hovedkildefilen til Basys 3 -kortet. Sørg for å kjøre syntese, implementering og generere bitstream -kontroll for eventuelle feil. Hvis alt kjøres vellykket, åpner du maskinvarebehandleren og programmerer Basys 3 -enheten. Prosjektet ditt er nå fullført!

Anbefalt:

Automatiske gatelys ved bruk av ultralydsensor: 3 trinn

Automatiske gatelys ved bruk av ultralydsensor: Trodde du noen gang at hvordan gatelysene automatisk slås på om natten og slås AV automatisk om morgenen? Er det noen som kommer til PÅ/AV disse lysene? Det er flere måter å slå på gatelys på, men følgende

Hvordan lage automatisk gatelys ved hjelp av LM555 IC: 8 trinn

Hvordan lage automatisk gatelys ved bruk av LM555 IC: Hei venn, I dag skal jeg lage en krets med automatisk gatelys ved hjelp av LM555 IC. Denne kretsen fungerer slik Når lyset faller på LDR (på dagen), så lyser ikke LED -en og når lyset ikke vil være på LDR, lyser LED automatisk

Hvordan lage automatisk gatelys: 7 trinn

Hvordan lage automatisk gatelys: Hei venn, I dag skal jeg lage en krets med automatisk gatelys. Denne kretsen vil fungere automatisk. Om morgenlyset vil den stenge automatisk. Denne kretsen jobber med LDR. La oss komme i gang

Bevegelsesaktiverte trapper: 6 trinn (med bilder)

Bevegelsesaktiverte trapper: Ja, jeg vet hva du tenker, dette virker litt overkill, men først og fremst trenger du aldri å bekymre deg for å stikke tåen igjen, og for det andre, det gjør å gå opp og ned trappene så mye gøy, jeg fant meg selv ovenpå uten grunn

Energieffektiv datamaskin: 9 trinn

Energieffektiv datamaskin: Det finnes utallige instrukser og artikler om hvordan du bygger din egen PC. Imidlertid er det ikke så mange guider for å bygge en PC som er energieffektiv. Gjennom hele denne instruksen vil jeg gi deg noen tips om hvordan du velger