Innholdsfortegnelse:

- Trinn 1: Blokkdiagram

- Trinn 2: Driftsprinsipp

- Trinn 3: Logisk implementering

- Trinn 4: Løse dødsfall

- Trinn 5: Enhetskonfigurasjon - Matrix0 Circuit

- Trinn 6: Enhetskonfigurasjon - SPI Clocking Logic

- Trinn 7: Enhetskonfigurasjon - Egenskaper for Matrix0 -komponenter

- Trinn 8: Enhetskonfigurasjon - Matrise1 -krets

- Trinn 9: Enhetskonfigurasjon - 3 -biters binær teller

- Trinn 10: Enhetskonfigurasjon - 3 -bits sammenligningslogikk

- Trinn 11: Enhetskonfigurasjon - Digital sammenligningslogikk og midlertidig register

- Trinn 12: Enhetskonfigurasjon - Egenskaper for Matrix1 -komponenter

- Trinn 13: Resultater

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:21.

- Sist endret 2025-01-23 15:02.

Kontrollsystemer og relaterte enheter håndterer flere strømkilder, for eksempel forspenningslinjer eller batterier, og må spore den høyeste (eller laveste) linjen blant et gitt sett.

For eksempel krever lastbytte i et "multi-batteri" -drevet system at systemet overvåker enten minimum eller maksimal spenning blant batterimassen (maks eller min som en funksjon av den bestemte koblingsalgoritmen) og dynamisk dirigerer lasten til mest passende kilde i sanntid. Alternativt kan det hende at systemet må koble fra det laveste spenningsbatteriet midlertidig for riktig lading.

Et annet eksempel er det moderne solenergisystemet, hvor hvert solcellepanel er utstyrt med en tiltrotatmekanisme og med en solar tracking -krets (sistnevnte gir informasjon om solens posisjon for å orientere panelet). Med informasjon om maks spenning kan hver solcellepanelposisjon finjusteres på grunnlag av at strengens panel faktisk leverer den høyeste utgangsspenningen, og dermed oppnå et overlegen nivå av effektoptimalisering.

Det er flere forskjellige merker av kommersielle IC -er (hovedsakelig mikrokontrollere) som i prinsippet kan implementere en maksimal spenningsfølger. Imidlertid krever de programmering og er mindre kostnadseffektive enn en løsning med blandet signal. Å supplere en Dialog GreenPAKTM -design kan positivt påvirke designens overkommelighet, størrelse og modularitet. Denne designen utnytter fordelen ved å integrere både analoge og digitale kretser i en enkelt brikke.

I denne instruksjonsboken er den analoge fronten og den digitale logikken som kreves for å implementere en maks (eller til slutt min) spenningssøker blant åtte forskjellige kilder implementert.

For å implementere den 8-kanals analoge maks/min spenningsmonitoren brukes en SLG46620G.

Nedenfor har vi beskrevet trinnene som trengs for å forstå hvordan løsningen er programmert til å lage 8-kanals analog maks/min spenningsmonitor. Men hvis du bare vil få resultatet av programmeringen, kan du laste ned GreenPAK -programvare for å se den allerede fullførte GreenPAK -designfilen. Koble GreenPAK Development Kit til datamaskinen din og trykk på programmet for å lage 8-kanals analog maks/min spenningsmonitor.

Trinn 1: Blokkdiagram

Figur 1 viser det globale diagrammet over det implementerte systemet.

En streng på opptil 8 variable spenningskilder blir multiplekset og grensesnittet til en GreenPAKs ADC -modul koblet til en tilpasset intern design som er i stand til å velge kilden med den høyeste spenningen i forhold til de andre. Den interne logikken sender ut denne informasjonen for visning eller videre behandling.

Designet er basert på GreenPAK SLG46620G -produktet, fordi det bygger inn alle nødvendige analoge og digitale byggesteiner for applikasjonen. I denne implementeringen skannes matrisen ved hjelp av en ADG508 analog multiplexer direkte drevet av GreenPAK IC.

Utgangsinformasjonen er et 3-bits digitalt tall som tilsvarer spenningskildetallet ved maks spenning. En direkte måte å få denne informasjonen på er å vise tallet ved hjelp av et 7-segmenters display. Det kan enkelt oppnås ved å koble SLG46620Gs digitale utgang til en 7-segmenters skjermdriver, for eksempel GreenPAK-løsningen beskrevet i Reference eller en vanlig 74LS47 IC.

Kretsen som presenteres ser etter maksimal spenning. For å konvertere designet til en minimumsspenningssøker må det legges til en enkel prekondisjoneringskrets mellom den analoge multiplexeren og den grønne PAK-inngangen, og trekker multiplexerutgangen fra en 1 V referansespenning.

Trinn 2: Driftsprinsipp

Designet tar sikte på å velge kilden med maks spenning, derfor utføres en skanning på hele matrisen mens den siste maks-verdien lagres og sammenlignes med den neste verdien i inngangen (som tilhører den neste spenningskilden i skanningen).

I det følgende vil vi referere til en komplett multipleksingssekvens langs alle inngangene som en "skanning" eller "sløyfe".

Sammenligning mellom to verdier oppnås ikke ved hjelp av ACMP -komponenter (er imidlertid tilgjengelig i SLG46620G), men heller med DCMP -modulen, når verdiene er henholdsvis digitalisert. Dette er en avansert og raffinert teknikk som først ble omtalt i Reference.

Figur 2 viser hvordan SLG46620G er strukturert for denne designen.

Det analoge inngangssignalet går til ADC-inngangen via PGA-komponenten med en angitt forsterkning på 1. Ulike forsterkningsinnstillinger er også mulig for å finne den beste matchen med front-end-kondisjoneringselektronikken som er viet til å kartlegge inngangsspenningene til 0-1 V utvalg av GreenPAK ADC -modulen.

ADC opererer i single-ended modus og konverterer det analoge signalet til en 8-bits digital kode, som deretter overføres til DCMP-modulen. Den digitale koden mates også inn i SPI -blokken, konfigurert som en ADC/FSM -buffer, hvor en digital kode kan lagres og ikke vil endres før neste puls kommer til SPI CLK -inngangen. Legg merke til at en dedikert logikkblokk driver SPI CLK -inngangen. Vi vil undersøke denne delen senere, siden dette er "kjerne" -logikken som er ansvarlig for riktig drift. En ny digital kode lagres bare i SPI -modulen hvis den tilhører den faktiske maksimale inngangsspenningen.

DCMP -komponenten brukes til å sammenligne nåværende ADC -data med den siste vinneren (det er den siste maksimal funnet) som er lagret i SPI -blokken. Det vil generere en puls ved OUT+ -utgangen når nye ADC -data er større enn den forrige. Vi bruker OUT+ -signalet til å oppdatere SPI -blokken med den nye vinneren.

Et globalt klokkesignal driver ADC -konverteringer og generelle tidspunkt. Når en konvertering er utført, pulserer ADCs INT -utgangssignal, koordinert i tide med ADCs parallelle datautgang. Vi bruker også INT-utgangen til å øke en 3-bits binær teller, implementert av DFF-er i Matrix1, noe som er nyttig av tre grunner:

1. Tellerutgangslinjene adresserer den eksterne analoge multiplexeren, og serverer dermed den neste inngangsspenningen til ADC;

2. Tellingen er frosset ned i et 3-biters register (implementert i Matrix1) for å lagre den midlertidige vinneren under en skanning;

3. Tellingen dekodes for å oppdatere et andre 3-biters register (implementert i Matrix0) når en skanning er fullført.

Trinn 3: Logisk implementering

ADC -modulen gir sekvensielt konverterte data for alle inngangsspenningene, en etter en, på ubestemt tid. Når multiplexeren er adressert 0b111 (desimal 7), ruller telleren av til 0b000 (desimal 0) og starter dermed en ny skanning av inngangsspenningene.

Under skanningen genereres ADC INT -utgangssignalet når den parallelle datautgangen er gyldig. Når dette signalet pulserer, må den analoge multiplexeren bytte til neste inngang, og gi PGA den tilsvarende spenningen. Derfor er ADC INT-utgangen det direkte klokkesignalet til den 3-bits binære telleren i figur 2, hvis 3-bits parallelle utgangsord direkte adresserer den eksterne analoge multiplexeren ("V select" i figur 1).

La oss nå referere til et eksempel der inngangsspenningene skal ha følgende forhold:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Figur 3 representerer hovedsignalene som er involvert i maks-beslutningsmekanismen.

Siden data til slutt klokkes inn i SPI -bufferregisteret synkront med INT -pulser, eksisterer det et sammenligningsvindu der SPI -bufferinnholdet sammenlignes med det neste ADC -konverteringsresultatet. Denne spesielle timingen resulterer i generering av OUT+ pulser ved DCMP -utgangen. Vi kan dra nytte av disse pulser for å laste inn nye verdier i SPI -bufferregisteret.

Som det fremgår av SPI -bufferdatalinjen i foregående figur, inneholder SPI -registeret alltid gang på gang den største verdien blant de 8 inngangene, og den oppdateres bare når en større verdi oppdages av DCMP -modulen (refererer til DCMP OUT+ utgangslinje for plottet, de manglende impulsene får V2 til å forbli låst i registeret til det sammenlignes med V5).

Trinn 4: Løse dødsfall

Hvis den implementerte logikken ville være akkurat som beskrevet ovenfor, er det klart at vi ville støte på en fastlåst situasjon: systemet er i stand til å oppdage bare spenninger høyere enn den som tilsvarer det som er lagret i SPI -bufferregisteret.

Dette er også gyldig i tilfelle denne spenningen reduseres og deretter en annen inngang, til nå lavere enn det, blir den høyeste: den ville aldri bli oppdaget. Denne situasjonen forklares bedre i figur 4 hvor bare 3 inngangsspenninger er tilstede av hensyn til klarhet.

På tidspunktet for iterasjon 2 faller V3 og V1 er den faktiske maks spenningen. Men DCMP -modulen gir ikke en puls fordi dataene som er lagret i SPI -bufferregisteret (tilsvarende 0,6 V) er større enn det som tilsvarer V1 (0,4 V).

Systemet oppfører seg da som en "absolutt" maksimalfinner og oppdaterer ikke utgangen riktig.

En fin måte å overvinne dette problemet på er å tvinge omlasting av data til SPI -bufferregisteret når systemet fullfører en full avstemningssyklus for alle kanaler.

Faktisk, hvis spenningen ved den inngangen fortsatt er den høyeste, endres ingenting og kontrollen fortsetter trygt (med henvisning til figur 4 ovenfor, er dette tilfellet med Loop Iterations 0 og 1). På den annen side, hvis spenningen ved den inngangen ved en tilfeldighet senkes til en verdi som er mindre enn en annen inngang, gir omlasting av verdien muligheten til DCMP -modulen til å produsere en OUT+ puls når den sammenlignes med den nye maksverdien (dette er tilfelle av Loop Iterations 2 og 3).

Et stykke logikkrets er nødvendig for å overvinne problemet. Den må generere et klokkesignal til SPI-komponenten når sløyfen når den faktiske maksimale inngangen, og dermed tvinge en ny innlasting av det oppdaterte dataordet til SPI-bufferregisteret. Dette vil bli diskutert i avsnitt 7.2 og 7.6 nedenfor.

Trinn 5: Enhetskonfigurasjon - Matrix0 Circuit

SLG46620G har to Matrix -blokker, som vist på figur 2. De følgende figurene viser de respektive enhetskonfigurasjonene.

Den øvre delen av kretsen er "Loop Register" realisert med 3 DFFs (DFF0, DFF1 og DFF2). Det oppdateres etter hver sløyfe i inngangsmultiplekseren for å sende det binære nummeret til “vinneren” til en sjefsegmentdriver, det vil si inngangen med høyeste spenning i den siste skanningen. Både klokken til DFF -ene og dataene kommer fra logikken implementert i Matrix1 gjennom henholdsvis port P12, P13, P14 og P15.

Den nedre delen er den analoge frontenden med inngang på Pin 8 og PGA med gain x1. ADC INT -utgangen går både til SPIs kloklogikk og til Matrix1 via port P0, hvor den vil fungere som klokkesignal for telleren som er implementert.

ADC og SPI parallelle datautganger er henholdsvis merket NET11 og NET15 for å være koblet til DCMP -komponenten i Matrix1.

Trinn 6: Enhetskonfigurasjon - SPI Clocking Logic

Som påpekt tidligere i delen "Logisk implementering", oppdateres SPI -bufferregisteret hver gang en sammenligning mellom den faktiske lagrede verdien og de nye ADC -konverteringsdataene genererer en puls ved DCMP OUT+ -utgangen.

Signalintegritet er sikret hvis dette signalet er AND-ed med ADC INT-utgangen. Dette unngår topp og falsk utløsning.

Vi har også understreket at SPI -bufferen må oppdateres når løkken når de faktiske vinnerdataene for å hoppe over fastlåsesituasjoner.

Tre signaler er deretter i spillet for riktig SPI -klokke:

1. ADC INT-utgang (LUT0-IN1)

2. DCMP OUT+ utgang (LUT0-IN0 via port P10)

3. Tell er lik Latch-signal (LUT0-IN2 via port P11)

De to første er AND-ed og begge OR-ed med sistnevnte i LUT0, hvis implementering er konfigurert som i figur 6.

Trinn 7: Enhetskonfigurasjon - Egenskaper for Matrix0 -komponenter

Figurene 7-10 viser de gjenværende vinduene til komponentegenskapene som tilhører Matrix0.

Trinn 8: Enhetskonfigurasjon - Matrise1 -krets

Trinn 9: Enhetskonfigurasjon - 3 -biters binær teller

Den øvre delen av kretsen inneholder logiske elementer, hovedsakelig en 3-bits binær teller klokket av ADC INT-utgangen, som allerede diskutert. Denne telleren er implementert med en ganske "standard" skjematisk vist i figur 12.

Denne telleren er realisert i vårt design ved hjelp av flip-flops DFF9, DFF10, DFF11 og INV1, LUT4, LUT8. DFF9 -utgangen er LSB mens DFF11 er MSB som vist på figur 13.

LUT4 er konfigurert som en XOR mens LUT8 utfører AND-XOR-logikken i figur 12.

Tellerutganger går til tre digitale utgangspinner for å adressere den eksterne analoge multiplexeren.

LUT10 dekoder tellerens kode når en skanning er fullført og mater en puls til Matrix0 via DLY8 og port P12. Dette oppnås ganske enkelt ved å AND-telle tellerens utganger, og dermed dekode nummer 7 des (0b111 binært, slutten av sløyfen).

Trinn 10: Enhetskonfigurasjon - 3 -bits sammenligningslogikk

Figur 15 viser kretsen som brukes til å oppdage når sløyfen gjentar seg ved den nåværende "vinner" -adressen. I dette tilfellet, som allerede diskutert, bør en digital puls tvinge en ny belastning av det nåværende ADC-resultatet til å løse en mulig dødsituasjon.

"Vinner" -adressen lagres i det midlertidige registeret til Matrix1 (se nedenfor), mens den nåværende adressen sendes ut av den binære telleren.

XNOR -porter gir en ekte (logisk 1 eller ‘høy’) utgang når begge inngangene er like. OG-ing av dette signalet for alle biter (LUT9) gir oss en puls når begge binære kodene er like. Detaljer om XOR -porter som paritetskontroll finnes i Reference.

Signalet ‘Counter-equals-Latch’ sendes til Matrix0 via port P11.

Trinn 11: Enhetskonfigurasjon - Digital sammenligningslogikk og midlertidig register

Den nedre delen av figur 11 (fremhevet i figur 16) viser DCMP-blokken, beslutningsdelen av dette designet.

DFF6, 7 og 8 danner et 3-biters register for å lagre det midlertidige inndatatallet “vinner” mens sløyfen kjører. Inngang til flip-flops er 3-biters binære tellerutganger, som synlig i den globale Matrix1-kretsen i figur 11, her hoppet over for klarhetens skyld.

Utganger fra dette registeret kan ikke styre 7-segmentskjermen direkte fordi verdien som er lagret her endres under en skanning og bare skal betraktes som "gyldig" på slutten av selve skanningen.

Av denne grunn kobler de midlertidige registerutgangene seg til Matrix0's Loop Register via intermatrise-porter P13, P14 og P15.

Det er viktig å observere i figur 16 at det midlertidige registeret blir klokka av DCMP OUT+ -utgangen når ADC-SPI registrerer sammenligning resulterer i en ny maks funnet.

Det samme OUT+ -signalet sendes til Matrix0, SPI CLK Logic, via port P10.

Trinn 12: Enhetskonfigurasjon - Egenskaper for Matrix1 -komponenter

Figurene 17-19 viser komponentegenskapsvinduene som tilhører Matrix1.

Trinn 13: Resultater

For å teste implementeringen har det blitt konstruert en evalueringstavleprototype, hvor de 8 analoge inngangsspenningene oppnås av en serie motstandsdelere med TrimPots (som vist i figur 20).

Multiplexeren som brukes er en ADG508, en del som kan fungere med en enkelt forsyning (12 V).

7-segmenters skjermdriver er en 74LS47. Den dekoder et parallelt inndata og driver direkte en 7-segment skjerm med felles anode.

Evalueringskortet har en 2x10 rettvinklet kontakt for å koble direkte til en GreenPAK Advanced Development Platform ved ekspansjonskontakten som vist i figur 21.

Sammen med GreenPAK Advanced Development Platform gjør det veldig enkelt å ta målinger av signalene for en rask sjekk. For eksempel viser figur 22 et sett med signaler (henholdsvis CLOCK, ADC INT -utgang og DCMP OUT+ -utgang) som fanget opp av en HP 54620A Logic Analyzer. Bølgeformer utløses av en stigende kant av OUT+ -signalet (på omfanget merket som ‘A> B’), og derfor er dette en bølgeformfangst når en ny maks spenning oppdages blant de analoge inngangene. Faktisk ble det oppnådd ved å rotere en av TrimPots på evalueringskortet for å øke den tilsvarende spenningen vist i figur 22.

Figur 23 viser skjematisk oversikt over evalueringsnemnda.

Konklusjon

I denne instruksjonsboken implementerte vi en åtte-kanals maks (eller min) spenningssøker som skal brukes som et vanlig tillegg til flerkanals kontrollsystemer. Den presenterte tilnærmingen utnytter avanserte funksjoner i GreenPAK -komponentene og viser hvordan det er mulig å integrere i en enkelt chip analoge og digitale funksjoner. Flere kommersielle IC -er kan erstattes med Dialog GreenPAK -er slik at applikasjonsstørrelsen og kostnaden kan reduseres.

Anbefalt:

Min DIY Peltier Cooler! DEKOMMISSJONERT: 9 trinn (med bilder)

Min DIY Peltier Cooler! - DEKOMMISSJONERT: Jeg har alltid ønsket et middel for å holde dagligvarer kjølig nok i bilen min uten å måtte skynde meg hjem til kjøleskapet mitt. Jeg bestemte meg for å bruke en gammel Peltier varmeveksler jeg laget for noen år siden. Jeg klemte Peltier mellom to kjøleribber i aluminium. Det store

Spenningsmonitor for høyspenningsbatterier: 3 trinn (med bilder)

Spenningsmonitor for høyspenningsbatterier: I denne veiledningen vil jeg forklare deg hvordan jeg bygde batterispenningsmonitoren for mitt elektriske longboard. Monter den slik du vil, og koble bare to ledninger til batteriet (Gnd og Vcc). Denne veiledningen antok at batterispenningen overstiger 30 volt

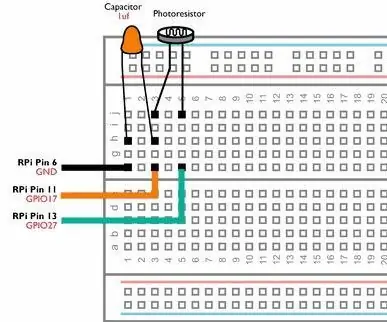

Raspberry Pi GPIO -kretser: Bruke en LDR analog sensor uten ADC (analog til digital omformer): 4 trinn

Raspberry Pi GPIO -kretser: Bruke en LDR -analog sensor uten ADC (analog til digital omformer): I våre tidligere instrukser har vi vist deg hvordan du kan koble din Raspberry Pi's GPIO -pinner til lysdioder og brytere og hvordan GPIO -pinnene kan være høye eller Lav. Men hva om du vil bruke din Raspberry Pi med en analog sensor? Hvis vi vil bruke en

Batteritransplantasjon, resirkulering til maks: 5 trinn

Batteritransplantasjon, resirkulering til maks: Mens jeg rengjorde verkstedet mitt, fant jeg et par DeWALT -batterier som var helt døde. De ville ikke ta en ladning, og å zappe dem med høyspenning fungerte ikke eter. Siden de fleste av verktøyene mine er DeWALT har ekstra batterier nyttig

Picaxe -basert digitalt termometer med maks og min: 13 trinn

Picaxe-basert digitalt termometer med maks og min: (Vennligst legg igjen en melding, men ikke vær for kritisk, dette er min første instruerbare !!) Dette er et termometer jeg laget for bobilen vår, for å vise utetemperaturen. Den er basert på en Picaxe -brikke siden de er billige og enkle å bruke. Hvis dette er for