Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:20.

- Sist endret 2025-01-23 15:02.

JDM er en populær PIC -programmerer fordi den bruker en seriell port, et minimum av komponenter og krever ingen strømforsyning. Men det er forvirring der ute, med mange programmeringsvariasjoner på nettet, hvilke fungerer med hvilke PIC -er? I denne "instruerbare" tester vi JDM, og jeg demonstrerer hvordan du kan simulere kretsen ved hjelp av Spice som vil svare på alle spørsmålene dine!

Rekvisita

LTspice som kan lastes ned fra analoge enheter her.

Du trenger også JDM -kretsfilene her.

Trinn 1: Krav til serieport

JDM krever en seriell port som oppfyller EIA232-spesifikasjonen, ideelt sett med +12/-12 spenningsnivåer.

I følge Texas Instruments Line Driver MC1488 datablad (figur 3)

Utgangsimpedans = 4V/8mA = 500 ohm.

Kortslutningsstrømgrense = 12mV, uten tidsbegrensning - ingen skade på brikken.

Inngangsimpedans for linjemottaker = 3k til 7k ohm anbefalt.

Serielle porter på eldre stasjonære PCer bruker +12v/-12V som oppfyller dette kravet.

Serielle porter på nyere bærbare PC -er bruker lavere spenninger. JDM fungerer kanskje eller ikke - svaret er mer komplekst.

Trinn 2: Krav til programmering av PIC

Informasjon om PIC -programmeringskrav er hentet fra Microchip. Ovenstående er for en typisk enhet.

Trinn 3: JDM -spesifikasjon

Har det opprinnelige JDM -nettstedet gått tapt i tidens tåker? Dette lar oss gjette hva designeren opprinnelig hadde til hensikt med spesifikasjonen.

- Gi VDD = 5V, og opptil IDD = 2mA maksimum (for "in socket" -versjon)

- Gi VHH = 13V, og opptil IHH = 0,2mA maks.

- MCLR Stigningstid tVHHR = 1uS maks.

- ICSP-versjonen må kunne trekke MCLR lavt mot 22k pull-up på målet.

Trinn 4: Kretsbeskrivelse

Figur JDM1 er basert på den "standard" JDM -kretsen hentet fra PICPgm -nettstedet. Dette er "PIC in Socket" programmereren der PIC tar strøm fra TX og RTS pins. Det originale diagrammet var vanskelig å forstå, så jeg har tegnet det på nytt ved å bruke den vanlige strømmen fra topp til bunn. Og jeg har lagt til LED -indikatorer “RESET”, “PROG” og “RTS” som er nødvendige under konstruksjon og testing. Forhåpentligvis har disse ikke noen skadelig effekt på atferd.

Den vanlige konvensjonen for kretsdesign er felles alle grunner, men hovedtrekk ved JDM er at seriell portjord (GND) er koblet til VDD. Dette skaper forvirring ettersom serielle portsignaler måles med hensyn til GND, PIC -signaler med hensyn til logisk bakken (VSS).

Når TX går høyt, oppfører Q1 seg som to forspenningsdioder. (Q1 -kollektoren er ikke omvendt forspent som ved normal transistordrift). Samler Q1 lader C2, som klemmes ved VDD+8V av Zener (D3). Q1 -sender sender 13V til MCLR for Program/Verify Mode.

Når TX går lavt, lades kondensatoren C3 gjennom D1 og VSS klemmes fast ved VDD-5V av zener (D5). TX er også klemt til (VSS-0.6) med D1. Q1 er slått av, C1 holder ladningen for neste programmeringspuls. MCLR er klemt på 0V med D2, så PIC er nå Reset.

Når RTS er høy, sendes klokken til PGC. D4 klemme PGC ved VDD logikk høy. Når RTS er lav, lades kondensator C3 gjennom D6 og VSS klemmes ved VDD-5V med zener (D5). D6 klemmer PGC ved VSS eller logikk 0.

Under programmeringen leses data som sendes ut på DTR på PGD, som PIC konfigurerer som input. Når DTR er høy, fungerer Q2 som "emitterfølger" og PGD-spenningen er omtrent (VDD-0.6) eller logisk 1. Når DTR er lav, fungerer Q2 som en dårlig transistor (sender og kollektorpinner omvendt). Q2 trekker PGD lavt, som klemmes av D7 ved VSS eller logikk 0.

Under kontrollen konfigurerer PIC PGD som en utgang for å sende data til den serielle porten. DTR må settes høyt, og data leses på CTS. Når PGD -utgangen er høy, er Q2 av, CTS = DTR = +12V. Når PGD -utgangen er lav, er Q2 på. Q2 -samler trekker strøm (12V+5V)/(1k+1k5) = 7mA fra DTR, og trekker CTS lavt, til VSS.

Trinn 5: Forbered deg på simulering

Last ned LT -krydder, lagre og åpne kretsfilene (*.asc) som er gitt her. For å simulere kretsen må vi gi den noen innganger, og deretter "spore" utgangene. V1, V2 V3 simulerer 12V seriell port med utgangsimpedans R11, R12, R13.

- V1 genererer 2 programpulser på TX fra 0,5 ms til 4,5 ms

- V2 genererer burst av datapulser på DTR fra 1,5 til 4,5 ms

- V3 genererer burst av klokkeimpulser på RTS fra 0,5 til 3,5 ms

Komponentene V4, X1, R15 og R16 er alle en del av simuleringen.

- V4 genererer 2 pulser fra 2,5 til 4,5 ms for å verifisere data.

- Jumper X1 simulerer OUTPUT på PGD.

- R15, R16 simulerer "lasting" av PIC på VDD og MCLR.

Trinn 6: Modifikasjoner for ICSP

Figur JDM3 viser versjonen for programmering av "i krets". Modifikasjoner fra originalen er

- Erstatt ZIF -kontakten med ICSP -kontakt.

- PIC -en drives nå av forsyning til målkretsen (V5).

- Fjern 5V zener (D5).

- Den lille 100pF kondensatoren (C4) flyttes ved siden av PIC på målkretsen.

- Lysdioder tar strøm fra kretskortet der det er mulig.

- MCLR opptrekkmotstand (R10) og diode (D10) kreves på målkretsen.

- ADVARSEL. Målkortet må ha en "flytende" forsyning, helst et batteri.

- Ikke koble måljord (VSS) til datamaskin/PC -jord ved å koble til andre dataporter samtidig med JDM.

Etter å ha simulert JDM1, ble problemet med lang ladetid på C2 tydelig. Etter å ha lest Fruttenboel ser det ut til at C2 og Q1 ble lagt til som en modifikasjon av originalen. Jeg kan ikke tro hva C2 og Q1 er ment å gjøre bortsett fra å skape problemer. Så for JDM4 går vi tilbake til den eldre designen på Fruttenboel som er enkel og grei å forstå. D1 og D3/LED2 klemme MCLR mellom VSS og VDD+8V. Verdien på R1 er redusert til 3k3, akkurat nok til å lyse LED2 ved 12V.

JDM4 er også designet for å fungere med svakere serielle porter. Når TX går høyt (+9V), er TX nåværende kilde = (9-8)/(1k +3k3) = 0,2ma, akkurat nok til å trekke MCLR høyt, selv om det ikke er nok til å lyse LED2. Når TX går lavt (omtrent -7V), synker TX strøm = (9-7)/1k = 2mA. LED1 strøm = (7-2 for led)/(2k7) = 1,8mA. MCLR trekk ned strøm = 7-5,5/3k3 = 0,5mA.

Denne kretsen er også testet (JDM5-simulering) for å se hva som skjer med serielle porter +/- 7V minimum, der det ikke er nok spenning til å opprettholde VHH = 13V. Formålet med C1 blir nå tydelig, C1 skaper et kort +ve løft for MCLR, en 33us pigg på stigende kant av TX, tilstrekkelig lang nok til at PIC kan gå inn i programmeringsmodus, kanskje? Men fjern jumper X2 (deaktiver LED1) ettersom det ikke er nok strøm til å trekke MCLR lavt og belyse LED1 sammen. Når TX går lavt, synker TX strøm = (7V-5.5V)/(1k+3k3) = 0.3mA, akkurat nok til å trekke MCLR lavt opp mot pull-up R10.

Trinn 7: Simuleringsresultater

For å se grafikkfilene er det bedre å høyreklikke på koblingene nedenfor, og deretter velge "Åpne lenke i ny fane"

Simulering 1: spor av MCLR, VSS og RTS for original JDM1. Observasjon 1, 2 og 3 er umiddelbart synlige.

Simulering 2: spor av MCLR og VSS, og RTS for modifisert JDM2, som løser tidligere problemer.

Simulering 3: spor etter PGD, VSS og PGC for JDM2 som sender data i programmodus. Observasjon 4 ved 3,5 ms.

Simulering 4: spor av PGD, VSS og CTS for JDM2 i verifiseringsmodus (jumper X1 satt inn). OK

Simulering 5: spor av MCLR, VSS, PGD og PGC for JDM3. ICSP ved hjelp av strøm fra krets løser mange problemer.

Simulering 6: spor av MCLR, VSS, PGD og PGC for JDM4 med +/- 9V seriell port. MCLR stiger umiddelbart og fungerer fullt ut.

Simulering 7: spor av MCLR, VSS og TX for JDM5 med +/- 7V seriell port og jumper X2 fjernet. C1 skaper en +ve boost (pigg) på stigende kant av MCLR, omtrent tilstrekkelig til å skyve MCLR over TX til 13V.

Trinn 8: Konklusjoner

Spice er virkelig flink til å avsløre "skjulte hemmeligheter" for kretsoperasjon. Tydeligvis fungerer JDM -kretsen og er kompatibel med mange PIC -brikker, men følgende observasjoner avslører mulige begrensninger/kompatibilitetsproblemer/feil?

- Lang stigningstid for MCLR mens C2 lades til VPP på den første pulsen til TX. Mislykkes spesifikasjon 3.

- Den serielle porten lader C2 når TX går høyt og RTS går lavt. Men RTS har også jobben med å lade C3. Når begge forekommer samtidig skaper dette mer belastning på RTS, og dermed mister C3 ladningen (VSS stiger) ved 2 ms på simulering. Mislykkes spesifikasjon 1.

- C3 mister ladningen (VSS begynner å stige) etter at klokkepulsene stopper på 3,5 ms.

- Hva er formålet med C2, er det nødvendig i det hele tatt?

Løsninger

- Antagelig bruker PICPgm en programvare "work-round". Den må bruke en lang TX -puls for å forlade til C2, og deretter bare gå inn i programmeringsmodus etter den andre TX -pulsen? For simulering reduserte jeg verdien av C2 til 1uF for å gi en økningstid på 1 ms. Ikke en ideell løsning.

- Del C2 og C3 slik at de lader uavhengig. En liten modifikasjon til JDM2, C2 refereres til GND i stedet for VSS.

- Løst av JDM3. ICSP er mye mer pålitelig ettersom PIC drives av målkrets.

- JDM4 løser problem 1. Dette er en enkel design som eliminerer C2 helt.

Trinn 9: Og til slutt

Beviset på puddingen er i å spise. Denne JDM fungerer, så fortsett å bruke den.

Og mine anbefalinger er:

- bruk JDM2 for in -socket programmering og 12V serielle porter,

- bruk JDM4 for ICSP-programmerer og serielle porter over +/- 9V,

- bruk JDM4 med jumper X2 fjernet for serielle porter over +/- 7V.

Referanser:

Analog Devices LT krydder

picpgm

Fruttenboel

Følg flere PIC-prosjekter på sly-corner

Anbefalt:

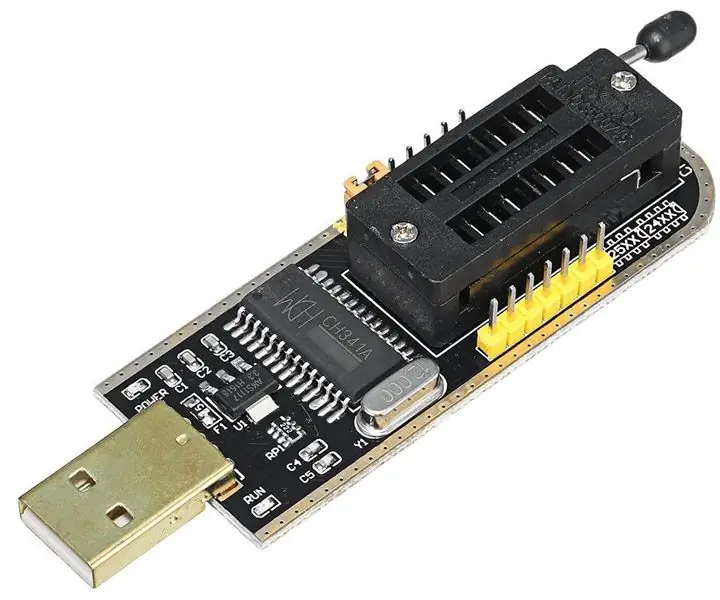

CH341A programmerer: 8 trinn

CH341A programmerer: Jeg har nylig kjøpt en CH341A mini programmerer. Miniprogrammereren er OK og kan brukes til å programmere sjetonger i 24 og 24 serier. Det er veldig lavt, men ganske nyttig, da jeg kan bruke det til å blinke datamaskinens BIOS og fastvare for ruteren

Arduino As ISP -- Brenn sekskantfil i AVR -- Sikring i AVR -- Arduino som programmerer: 10 trinn

Arduino As ISP || Brenn sekskantfil i AVR || Sikring i AVR || Arduino Som programmerer: ……………………… Vennligst abonner på YouTube -kanalen min for flere videoer …….. Denne artikkelen handler om arduino som isp. Hvis du vil laste opp hex -fil eller hvis du vil sette sikringen i AVR, trenger du ikke kjøpe en programmerer, du kan gjøre

Slik blinker eller programmerer du ESP8266 AT -fastvare ved hjelp av ESP8266 Blinker og programmerer, IOT Wifi -modul: 6 trinn

Slik blinker eller programmerer du ESP8266 AT-fastvare ved bruk av ESP8266 blinker og programmerer, IOT Wifi-modul: Beskrivelse: Denne modulen er en USB-adapter /programmerer for ESP8266-moduler av typen ESP-01 eller ESP-01S. Den er praktisk utstyrt med en 2x4P 2.54mm hunnhodet for å koble ESP01. Den bryter også ut alle pinnene på ESP-01 via en 2x4P 2.54mm hannh

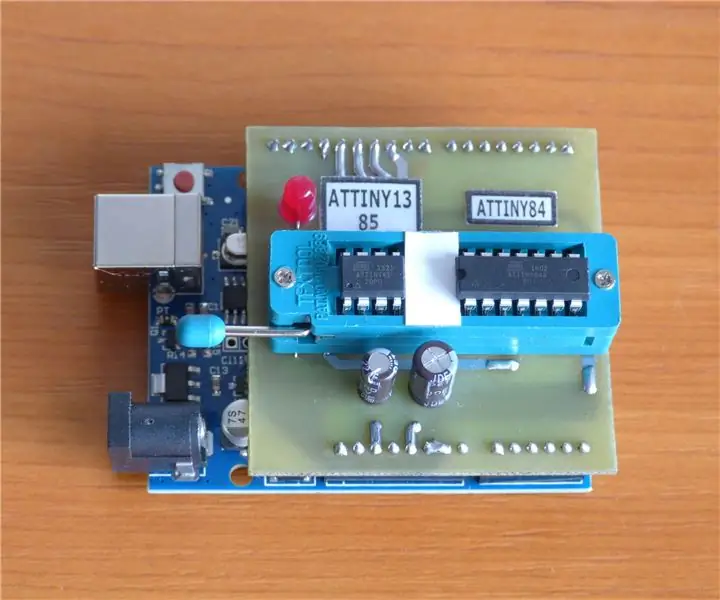

En liten programmerer for ATTINY mikrokontrollere med Arduino UNO: 7 trinn

En liten programmerer for ATTINY mikrokontrollere med Arduino UNO: Det er for tiden interessant å bruke mikrokontrollere i ATTINY -serien på grunn av deres allsidighet, lave pris, men også det faktum at de enkelt kan programmeres i miljøer som Arduino IDE. Programmer designet for Arduino -moduler kan være enkelt overføre

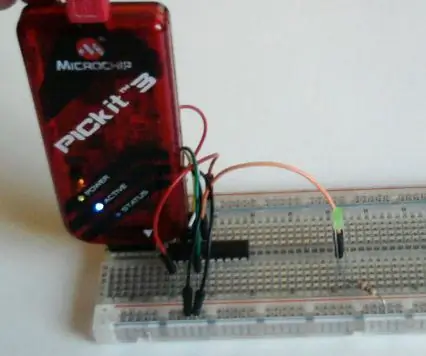

Slik programmerer du PIC MCU med PICkit -programmerer ved hjelp av et brødbrett: 3 trinn

Slik programmerer du PIC MCU med PICkit -programmerer som bruker et brødbrett: Du trenger ikke dyre og sofistikerte verktøy for å spille med PIC (eller andre) mikrokontrollere. Alt du trenger er et brødbrett der du tester kretsen og programmeringen. Selvfølgelig er en slags programmerer og IDE nødvendig. I denne instruksjonen