Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:22.

- Sist endret 2025-01-23 15:02.

Koble Mojo -utviklingsbordet til eksterne innganger med dette skjoldet.

Hva er Mojo utviklingstavle?

Mojo utviklingsbord er et utviklingsbord basert på Xilinx spartan 3 FPGA. Brettet er laget av Alchitry. FPGA er veldig nyttige der flere prosesser må utføres samtidig.

Hva trenger du?

Rekvisita

Mojo utviklingstavle

Gerber -fil

8 x 15k ohm motstander (valgfritt*)

4 x 470 ohm motstander

4 x 560 ohm motstander

4 x CC syv segment displayer

4 x 3 mm lysdioder

4 x SPDT taktile brytere

1 x 4 -posisjon overflatemonteret DIP -bryter

2 x 25 x 2 eller 4 x 25 overskrifter

1x 2 x 5 -pinners bokshode

Loddejern

Lodding

Flux

*(hvis disse motstandene utelates må intern pullup/nedtrekning være aktivert for relevante pinner)

Trinn 1: Last opp Gerber til PCB -produsenten du ønsker

For brettene mine bestilte jeg fra JLC PCB.

Den eneste endringen jeg gjorde var fargen jeg ønsket å matche den svarte på Mojo.

Trinn 2: Styremøte

Ved lodding er det alltid nyttig å lodde de laveste delene først, så det er en god idé å begynne med motstandene.

R5, R6, R7, R8, R9, R10, R11 og R12 er 15k ohm motstander som brukes til å trekke bryterne ned (hvis du bruker intern pullup/pulldown, ignorer dette).

R1, R2, R3, R4 er 560 ohm motstander som er ansvarlige for å begrense strømmen gjennom 7 segmenters display.

R13, R14, R15, R16 er 470 ohm motstander som er ansvarlige for å begrense strømmen gjennom de 4 lysdiodene.

Neste loddetinn dip -bryteren, taktile brytere, LED -er, syv segmentdisplayer og bokshodekontakt i den rekkefølgen.

Plasser nå 25 x 2 (eller 2 25 x 1) i mojo for å justere pinnene. Rett inn skjoldet med pinnene og lodd det på plass.

Trinn 3: Programvareoppsett

For programvare som refererer til Alchitry -nettstedet, gir deg beskjed om hva du trenger for å komme i gang og installere Xilinx ISE. Imidlertid endrer.ucf -filen slik at den vet hvilke pins som er koblet til det som er viktig for å få programmet til å kjøre.

Her er.ucf -filen jeg bruker med skjoldet:

KONFIG VCCAUX = 3,3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODE "clk" 50 MHz HØY 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Husk hvis du ikke har installert nedtrekksmotstandene for å redigere pinnene i.ucf med

| TREKKE NED; o

| PULLUP;

Hvis du vil bruke blokken til noe, er tilkoblingene som følger. Venstre er blokkeringsnummeret og høyre er mojo -pin -nummeret som du bør tilordne i.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pinne 4 = 41

pin 5 = 34

pin 6 = 35

pinne 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Anbefalt:

DIY ESP32 Development Board - ESPer: 5 trinn (med bilder)

DIY ESP32 Development Board - ESPer: Så nylig hadde jeg lest om mange IoT (Internet of Things) og stol på meg, jeg kunne bare ikke vente med å teste en av disse fantastiske enhetene, med muligheten til å koble til internett, meg selv og få tak i jobben. Heldigvis muligheten til

Spille Flappy Bird -spill med M5stack Esp32 -basert M5stick C Development Board: 5 trinn

Spille Flappy Bird Game With M5stack Esp32 Based M5stick C Development Board: Hei folkens i dag skal vi lære hvordan du laster opp flappy bird-spillkoden til m5stick c development board levert av m5stack.For dette lille prosjektet trenger du følgende to ting: m5stick-c utviklingstavle: https://www.utsource.net/itm/p/8663561.h

JALPIC One Development Board: 5 trinn (med bilder)

JALPIC One Development Board: Hvis du følger mine Instructables -prosjekter, vet du at jeg er en stor fan av programmeringsspråket JAL i kombinasjon med PIC Microcontroller. JAL er et Pascal-lignende programmeringsspråk utviklet for 8-biters PIC-mikrokontrollere av Microchip. Mo

Et AVR Development Board: 3 trinn

Et AVR Development Board: Internett er fullt av prosjekter med Arduino. For en stund mangler informasjonen om ATMEGA328 mikrokontroller i alle Arduino -dataene. Denne Insectructable ønsker å gjenopprette begynnelsen på hvordan man utvikler prosjekter ved hjelp av AVR -mikrokontakten

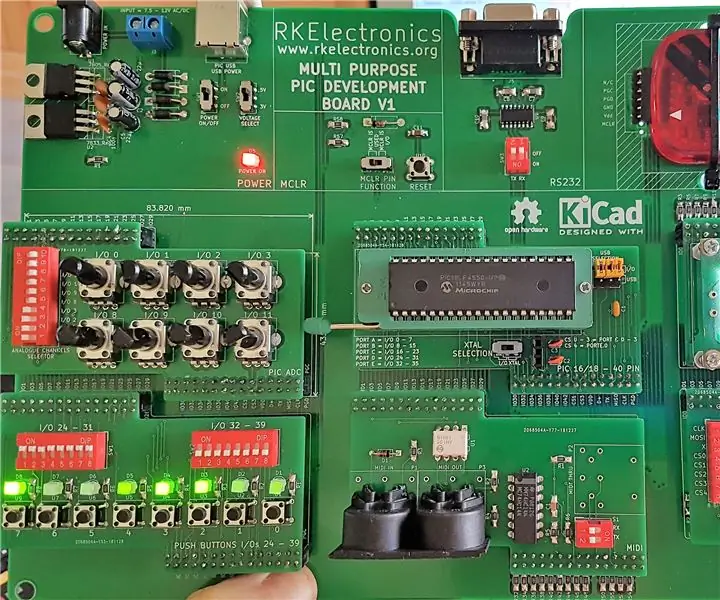

PIC Microcontroller Development Board System: 3 trinn

PIC Microcontroller Development Board System: Dette prosjektet er for design og bruk av et PIC -utviklingsverktøy som er fleksibelt for å passe til et bredt spekter av PIC -baserte elektroniske prosjekter. Det er ofte lettere å utvikle mikrokontrollerprosjekter ved bruk av utviklingsverktøy; som tillater brukerbasert