Innholdsfortegnelse:

- Forfatter John Day day@howwhatproduce.com.

- Public 2024-01-30 11:22.

- Sist endret 2025-01-23 15:02.

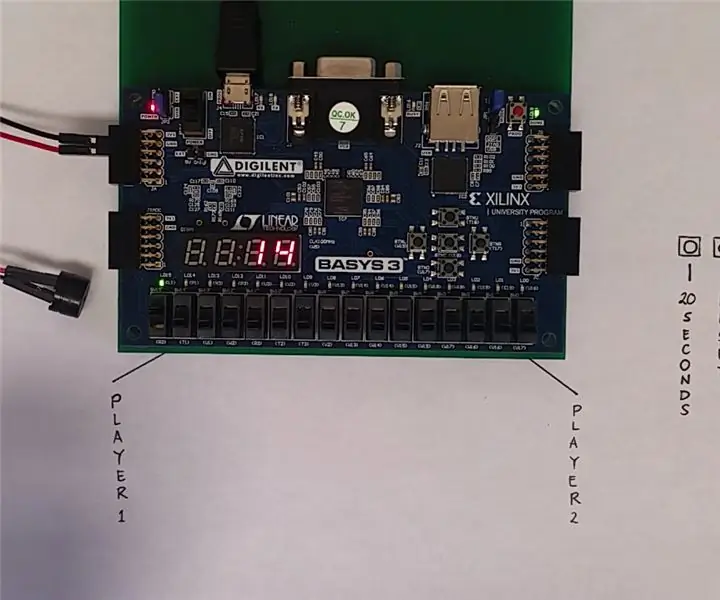

Det konkurrerende summer systemet designet i dette prosjektet fungerer på samme måte som summer systemene som brukes i Regional og National Science Bowl Competitions. Dette prosjektet ble inspirert av mitt engasjement i mitt videregående skoles team i tre år. Vi har alltid hatt et ønske om å gjenskape låsesummeret med en timer på 5 sekunder og 20 sekunder.

For å gi litt bakgrunn om summer -systemet, er science bowl -summerne programmert til å legge inn maksimalt 8 spillere (med 8 separate summer). Når en summer er trykket, lyser den første persons summer for å indikere hvilken spiller som mottar spørsmålet. Resten av spillerne vil bli "låst ute", noe som betyr at summerne deres ikke vil svare før moderatoren tilbakestiller summer -systemet.

Etter at moderatoren har lest spørsmålene, vil han trykke på en knapp for å starte nedtellingstimeren som vil bli vist på displayet med syv segmenter. Etter et "oppkast" -spørsmål, kan moderatoren trykke på høyre knapp for å starte nedtellingen fra 5 sekunder. I mellomtiden, etter et "bonus" -spørsmål, kan moderatoren trykke på venstre knapp for å starte nedtellingen fra 20 sekunder. Når timeren når null, vil en lydsignal indikere at spilleren har gått tom for tid.

For å tilbakestille systemet og nedtellingstimeren kan moderatoren trykke på midtknappen. For å tilbakestille låsemekanismen og spillerens lysdioder må bryterne for spiller 1 og spiller 2 være lave.

Trinn 1: Materialer

Du trenger følgende:

- Basys3 -kort (eller tilsvarende FPGA -kort)

- Micro-B USB-kabel

- Høyttaler (jeg brukte en passiv høyttaler)

- 2 ledninger

- Programvare for å implementere på FPGA (jeg brukte Vivado)

- Konkurransedyktig summer -fil

Trinn 2: Black Box Diagram

Svart boks diagram viser innganger og utganger som vil bli brukt i dette summer systemet.

INNGANGER:

spiller1, spiller2 Disse inngangene er koblet til to brytere på Basys3 -kortet. For enkelhets skyld brukes bryterne lengst til venstre og høyre.

reset Senterknappen brukes til å representere reset -knappen.

count_down_20_sec Den venstre knappen brukes til å representere 20-sekunders timer-knappen.

count_down_5_sec Den høyre knappen brukes til å representere 20-sekunders timer-knappen. For å sikre at både 20-sekunders og 5-sekunders timer starter, holder du inne knappen til syv segmenter viser timeren.

CLK FPGA -kortet vil generere en klokke som går med en frekvens på 10 ns.

UTGANGER:

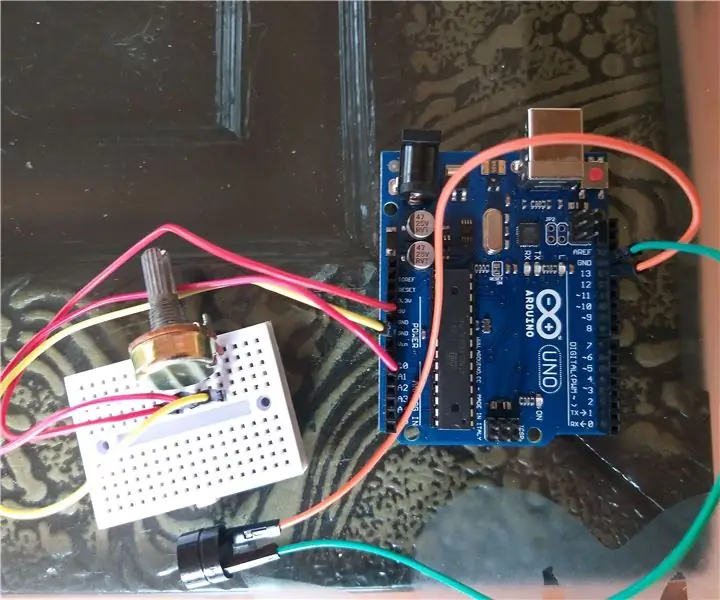

høyttaler Høyttalerutgangen er koblet til en ekstern summer eller høyttaler. Du må koble høyttaleren til Basys3 -kortet JA pmod -porter. Dette trinnet vil bli beskrevet nedenfor.

speaker_LED Denne utgangen er koblet til en LED på midten av brettet, og vil bare indikere når høyttalerutgangen til FPGA er høy. Du kan bruke dette til å teste den eksterne høyttaleren. Vær oppmerksom på at noen av pmod -portene kanskje ikke fungerer som de skal, så du kan prøve forskjellige og bruke LED -en til å kontrollere om høyttaleren skal være på.

SEGMENTER Denne utgangen er koblet til de åtte individuelle segmentene på displayet med syv segmenter, inkludert desimaltegnet.

DISP_EN Denne utgangen er koblet til de fire anodene på displayet med syv segmenter.

player_LED Denne utgangen er et 2-buntssignal som er koblet til lysdiodene over spiller1- og spiller2-bryterne. Den første spilleren som vender den tilhørende bryteren, vil bli indikert av LED -en. Vær oppmerksom på at begge lysdiodene ikke kan være på samtidig.

Trinn 3: Koble til den eksterne høyttaleren

For å koble den eksterne høyttaleren til Basys3 -kortet, ta de to ledningene og fest dem som angitt i bildet ovenfor. Den hvite linjen kobler den negative terminalen til høyttaleren til bakkeporten på brettet. Den røde linjen kobler den positive terminalen til høyttaleren til JA10 pmod -porten på kortet.

Begrensningsfilen er designet slik at enhver port fra JA1 til JA10 skal fungere. Noen pinner på brettet svarer imidlertid ikke, så hvis JA10 ikke fungerer, kan du prøve de andre portene.

Trinn 4: Strukturelt diagram

Bildet ovenfor viser konstruksjonsdiagrammet til det konkurransedyktige summer -systemet, inkludert alle komponentene som utgjør hovedmodulen. Beskrivelsene deres er som følger:

player_lockout_LED1 Spillerens lockout LED-komponent er en endelig tilstandsmaskin som bruker en-hot-koding. Den har fire innganger: player1, player2, reset og CLK. Den inneholder en 2-biters buntutgangsspiller_LED. Inngangene og utgangene til player_lockout_LED1-komponenten er alle direkte koblet til de identisk navngitte inngangene og utgangene til hovedmodulen.

buzzer_tone1 Summer -komponenten er basert på denne koden som er lagt ut på et forum

stackoverflow.com/questions/22767256/vhdl-… Den ble imidlertid modifisert for å sende en kontinuerlig lyd med en frekvens på 440 Hz (et notat). Aktivering -inngangen er koblet til et summer_enable -signal som er en utgang fra down_counter_FSM1 -komponenten.

clk_div1 Klokkeavdelerkomponenten er en modifisert versjon av professor Bryan Mealys klokkeskille på PolyLearn. Det bremser klokken slik at utgangsperioden er 1 sekund.

down_counter_FSM1 Nedtelleren er en FSM designet for å telle ned til null. De to mulige starttidene er 20 eller 5 som velges av brukerinngangen. Den sender ut '1' når timeren har nådd null for å indikere at tiden har gått ut. Denne utgangen fungerer som en aktivering for summertonekomponenten. Telleren sender også ut et 8-biters buntesignal som sender en 8-biters BCD som sendes til segmentdekoderen. En annen utgang er counter_on som også er koblet til den gyldige inngangen på segmentdekoderen.

sseg_dec1 Den syv-segmenters dekoder-komponenten er levert på PolyLearn og ble skrevet av professor Bryan Mealy. Den bruker en BCD-inngang levert av down_counter_FSM1, og sender ut desimalekvivalenten på sjusegmentsdisplayet. Når telleren er på, er den gyldige inngangen høy. Dette gjør at dekoderen kan vise desimaltallet på displayet med syv segmenter. Når telleren er slått av, er den gyldige inngangen lav. Den syv-segmenters displayet vil da bare vise fire streker.

Trinn 5: Finite State Machine (FSM) -diagram

Følsomhetslisten for finite state -maskinen inkluderer player1, player2, reset og klokken. FSM-utgangen er en 2-bits bunt player_LED koblet til to lysdioder på Basys3-kortet. Finite State Machine viser følgende tre tilstander:

ST0 er starttilstanden. I denne tilstanden er de to lysdiodene slått av. FSM vil forbli i denne tilstanden hvis både spiller1 og spiller2 er lave. En asynkron tilbakestilling setter også tilstanden til ST0. Når spiller1 -bryteren er satt til høy, vil neste tilstand være ST1. Hvis spiller2 -bryteren er satt til høy, vil neste tilstand være ST2.

ST1 er tilstanden som spiller1 -LED -en er på. FSM vil forbli i denne tilstanden for alle innspill. Dette betyr at selv når spiller2 -bryteren er satt til høy umiddelbart etter at spiller1 -bryteren er høy, vil den forbli i ST1. Bare den asynkrone tilbakestillingen kan sette den neste tilstanden til ST0.

ST2 er tilstanden som spiller2 LED er på. I likhet med ST !, vil FSM forbli i denne tilstanden for alle innganger, selv når spiller1 -bryteren er satt til høy umiddelbart etter at spiller2 -bryteren er høy. Igjen, bare den asynkrone tilbakestillingen kan sette den neste tilstanden til ST0.

Anbefalt:

Summer Fan Cooling Baseball Cap: 6 trinn

Summer Fan Cooling Baseball Cap: En dag da jeg rotet i garderoben min, så jeg en gammel rød baseballcap som jeg har kjøpt i fjor. Plutselig og en idé dukket opp i tankene mine, kunne jeg endre denne gamle hetten til et kult produkt som heter fan hat, et helt spesielt innovasjonsprodukt

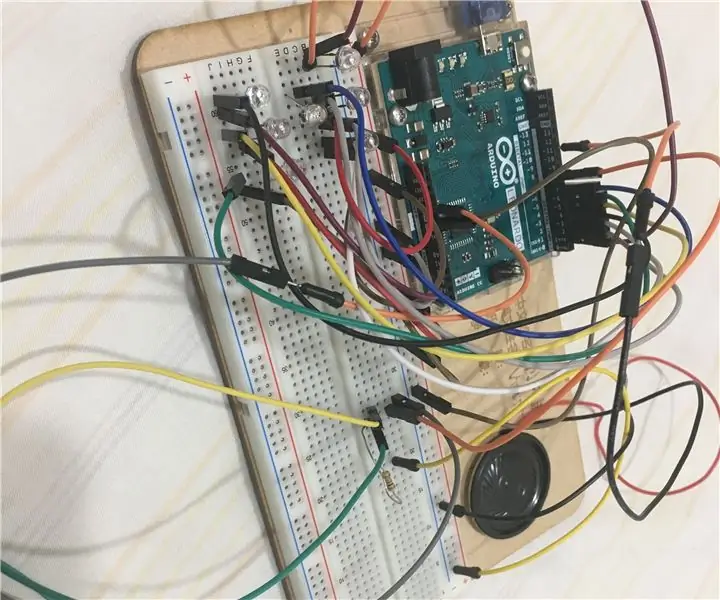

Super Mario ved hjelp av summer: 3 trinn

Super Mario Using Buzzer: Lytte til musikk slapper av sinn og sjel. La oss legge til litt musikk til dine arduino -prosjekter ved hjelp av en enkelt komponent, summer. Jeg fant dette fantastiske prosjektet ved hjelp av Buzzer som spiller super mario temasang skrevet av Dipto Pratyaksa på instruktører. I tillegg

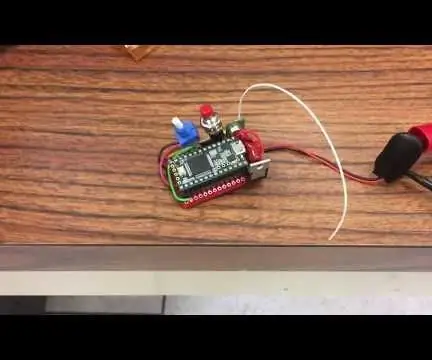

Fjernstyrt summer for tapt og funnet: 4 trinn

Fjernstyrt summer for tapt og funnet: Denne todelte kretsen består av en summer og en kontroller. Fest summeren til et element du ofte kan miste, og bruk knappen og volumknappen på kontrolleren for å aktivere summeren når elementet går tapt. Summeren og kontrollen

LED terninger med summer: 6 trinn

LED-terninger med summer: Denne instruksen vil lære deg hvordan du lager en LED-terning med summer når du trykker på knappen. Original kilde: https://www.instructables.com/id/Easy-Arduino-LED-Dice

Summer Wire Game: 4 trinn

Buzzer Wire Game: Wire summer -spillet som er kjent fra TV -serien til Mr.Bean er populært blant barn i alle aldersgrupper. Vi hadde som mål å få det til å skje med alle barna der ute. Dette enkle DIY -prosjektet består av lett tilgjengelige materialer og lave kostnader til